FlexRay Module Registers

www.ti.com

1408

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

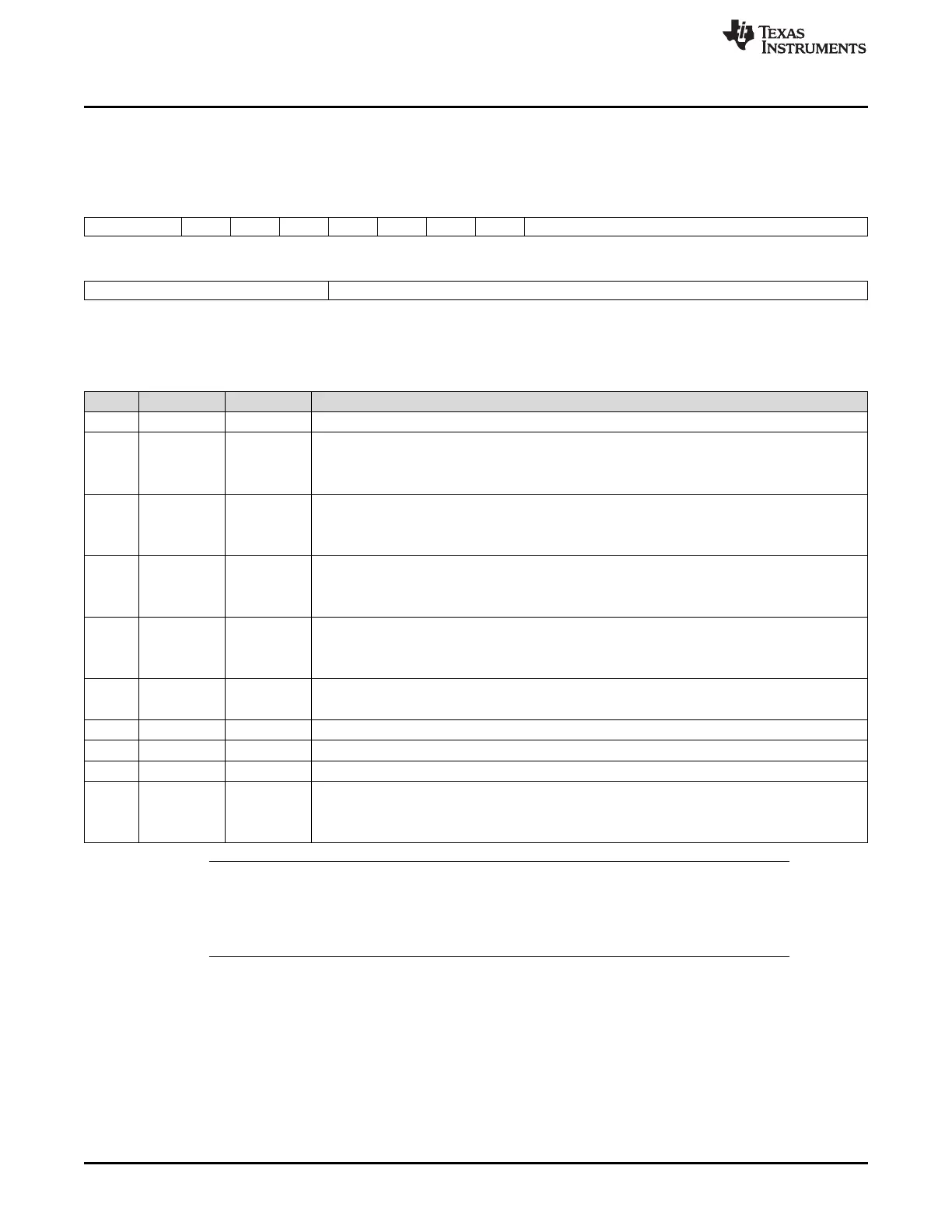

26.3.2.9.2 Read Header Section Register 1 (RDHS1)

Figure 26-187 and Table 26-160 illustrate this register.

Figure 26-187. Read Header Section Register 1 (RDHS1) [offset_CC = 700h]

31 30 29 28 27 26 25 24 23 22 16

Reserved MBI TXM PPIT CFG CHB CHA Rsvd CYC

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0

15 11 10 0

Reserved FID

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

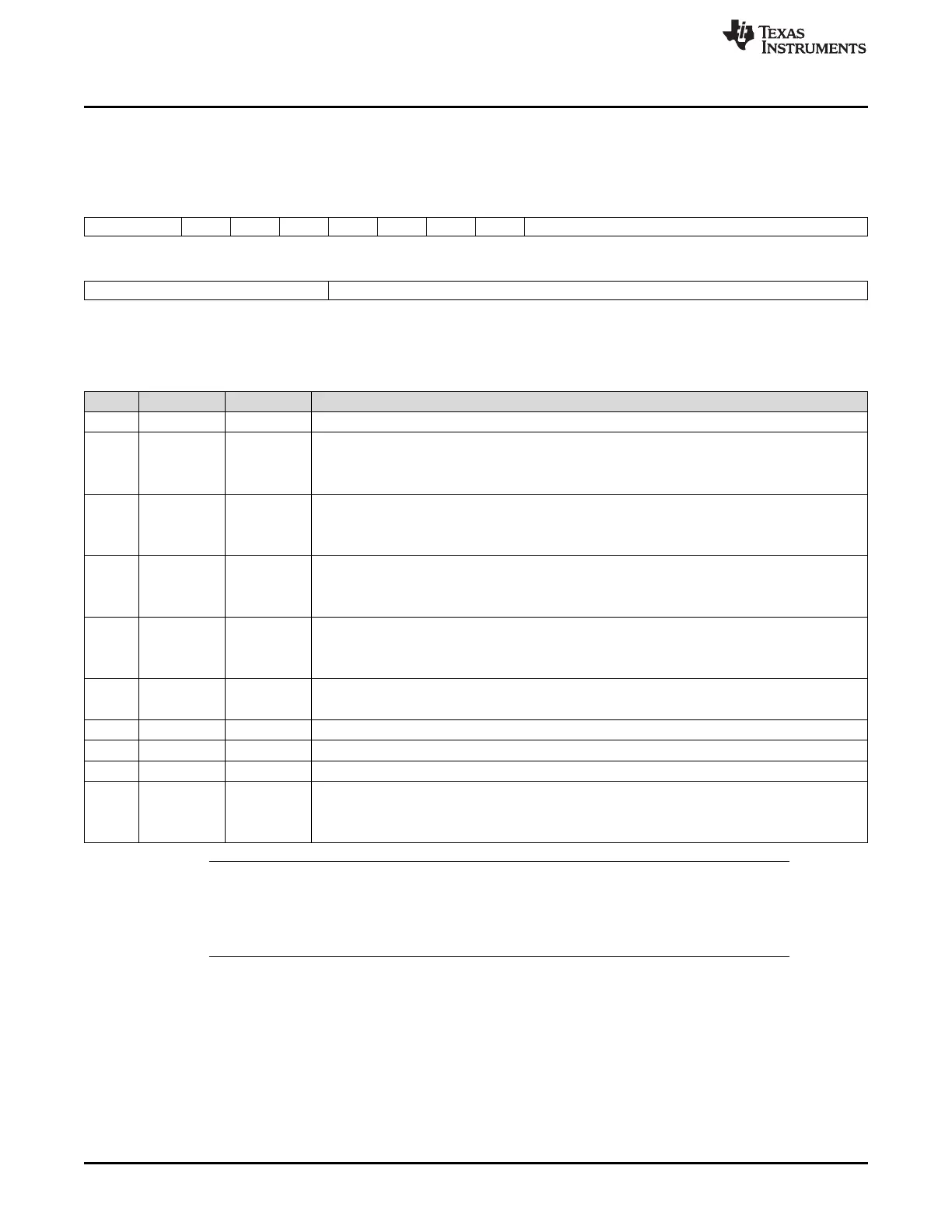

Table 26-160. Read Header Section Register 1 (RDHS1) Field Descriptions

Bit Field Value Description

31-30 Reserved 0 Reads return 0. Writes have no effect.

29 MBI Message buffer interrupt.

0 The corresponding message buffer interrupt is enabled.

1 The corresponding message buffer interrupt is disabled.

28 TXM Transmission mode. This bit is used to select the transmission mode.

0 Continuous mode.

1 Single-shot mode.

27 PPIT Payload preamble indicator transmit.

0 Payload Preamble Indicator is not set.

1 Payload Preamble Indicator is set.

26 CFG Message buffer configuration bit.

0 The corresponding buffer is configured as receive buffer.

1 The corresponding buffer is configured as Transmit buffer.

25-24 CHB, CHA Channel filter control.

See Table 26-154 for bit descriptions.

23 Reserved 0 Reads return 0. Writes have no effect.

22-16 CYC 0-7Fh Cycle code. The 7-bit cycle code determines the cycle set used for cycle counter filtering.

15-11 Reserved 0 Reads return 0. Writes have no effect.

10-0 FID 0-7FFh Frame ID.

Frame ID of the selected message buffer.

Note: Message buffers with frame ID = 0 are considered not valid.

NOTE: In case the message buffer read from the message RAM belongs to the receive FIFO, FID,

and CHA, CHB were updated from the received frame while CYC, CFG, PPIT, TXM, and

MBI are reset to 0.

For bit description, see also Section 26.3.2.8.2.

Loading...

Loading...