TC1796

Peripheral Units (Vol. 2 of 2)

Micro Second Channel (MSC)

User’s Manual 21-37 V2.0, 2007-07

MSC, V2.0

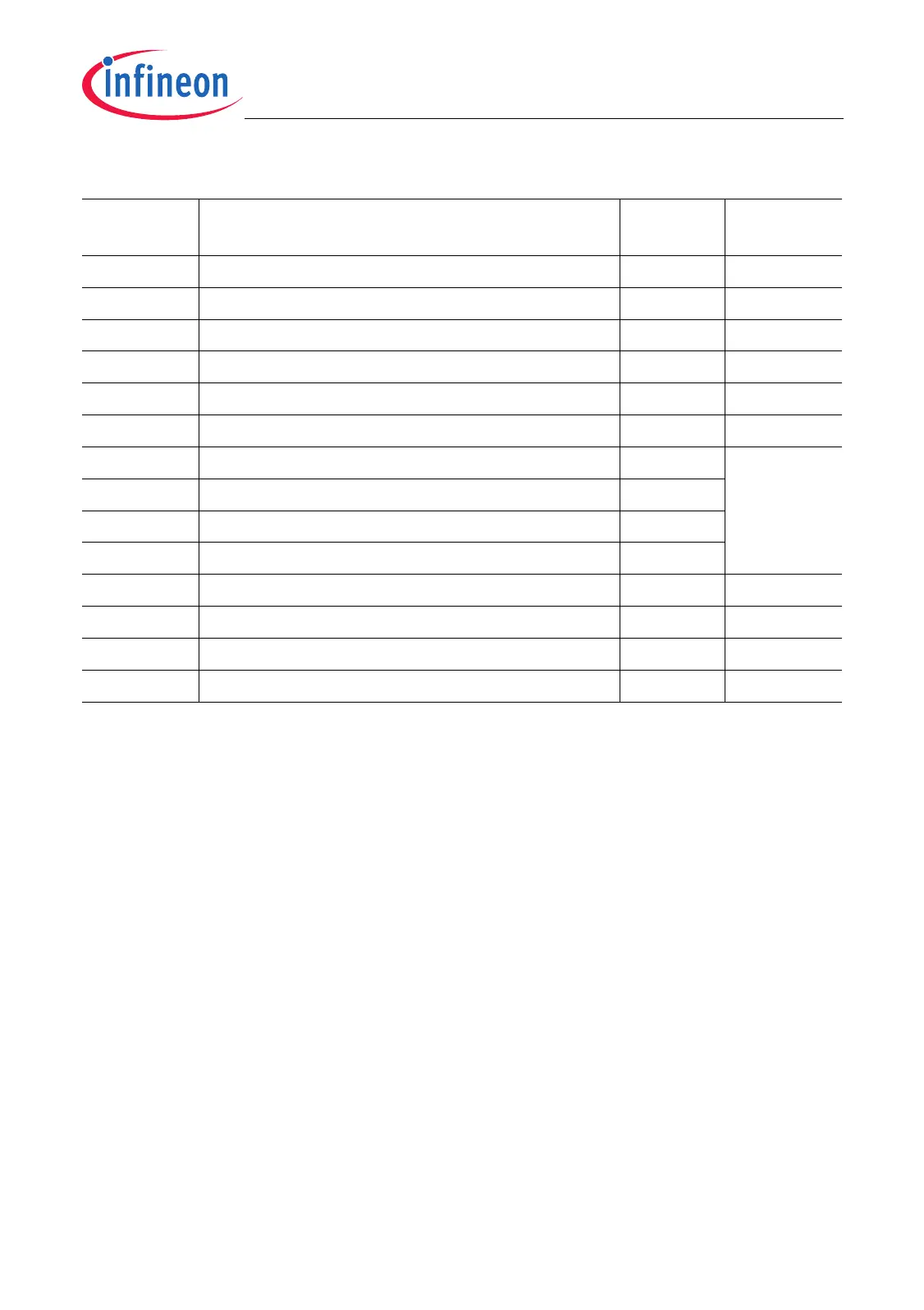

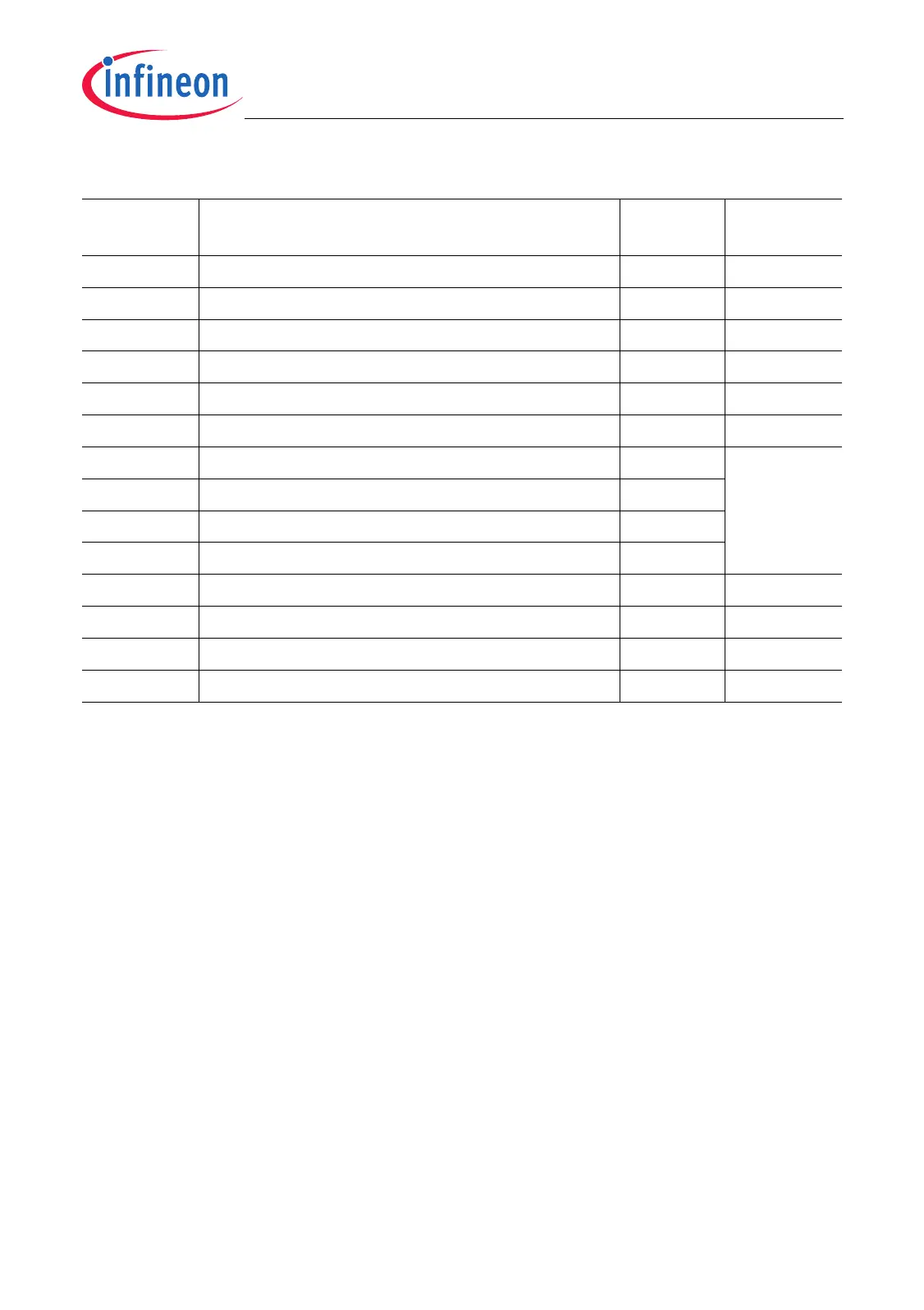

DSS Downstream Status Register 18

H

Page 21-44

DD Downstream Data Register 1C

H

Page 21-59

DC Downstream Command Register 20

H

Page 21-59

DSDSL Downstream Select Data Source Low Register 24

H

Page 21-46

DSDSH Downstream Select Data Source High Register 28

H

Page 21-47

ESR Emergency Stop Register 2C

H

Page 21-48

UD0 Upstream Data Register 0 30

H

Page 21-60

UD1 Upstream Data Register 1 34

H

UD2 Upstream Data Register 2 38

H

UD3 Upstream Data Register 3 3C

H

ICR Interrupt Control Register 40

H

Page 21-49

ISR Interrupt Status Register 44

H

Page 21-52

ISC Interrupt Set Clear Register 48

H

Page 21-54

OCR Output Control Register 4C

H

Page 21-56

1) The absolute register address is calculated as follows:

Module Base Address (Table 21-8) + Offset Address (shown in this column)

Table 21-9 Registers Overview - MSC Kernel Registers (cont’d)

Register

Short Name

Register Long Name Offset

Address

1)

Descriptio

n see

Loading...

Loading...