TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-28 V2.0, 2007-07

FADC, V2.0

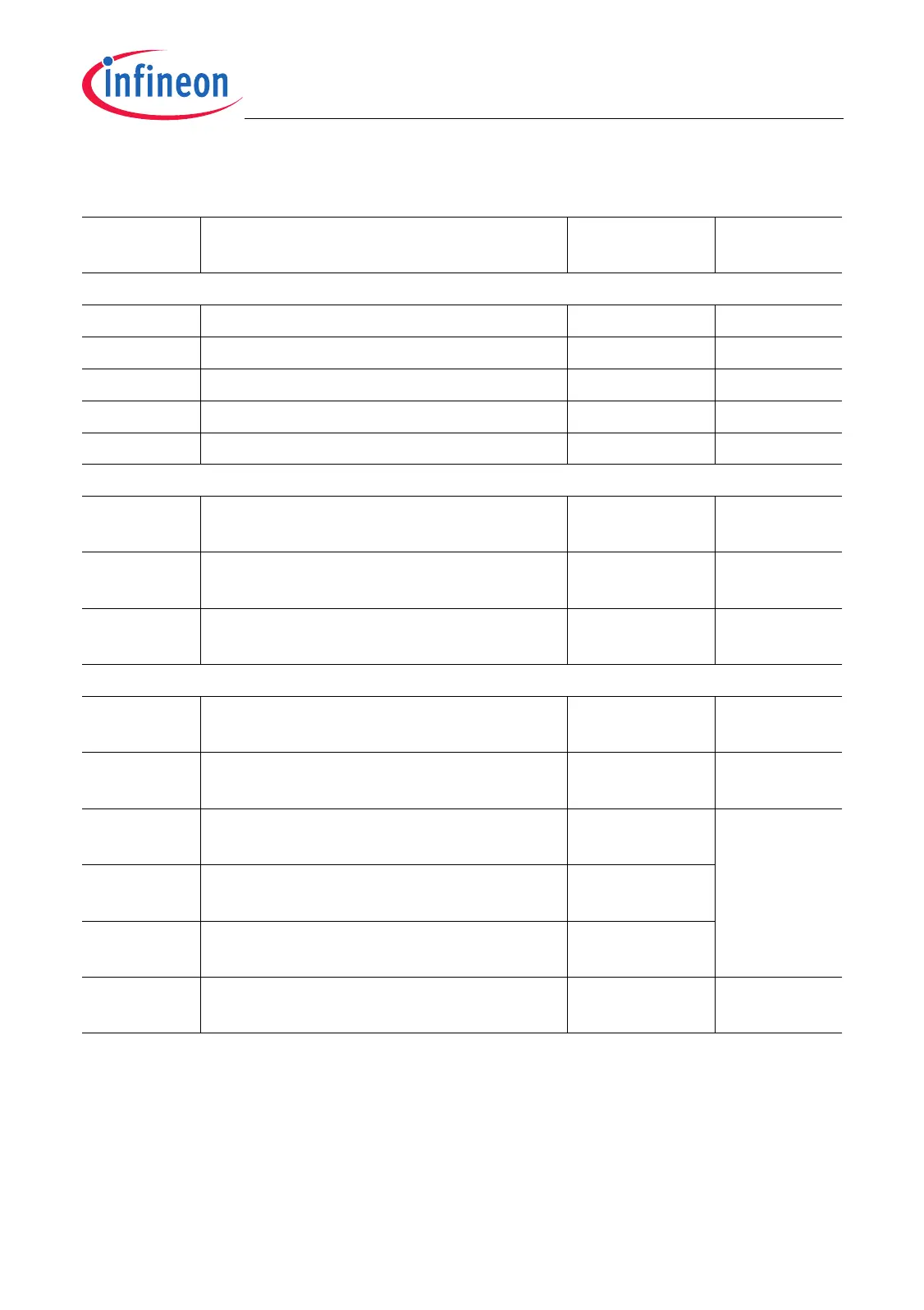

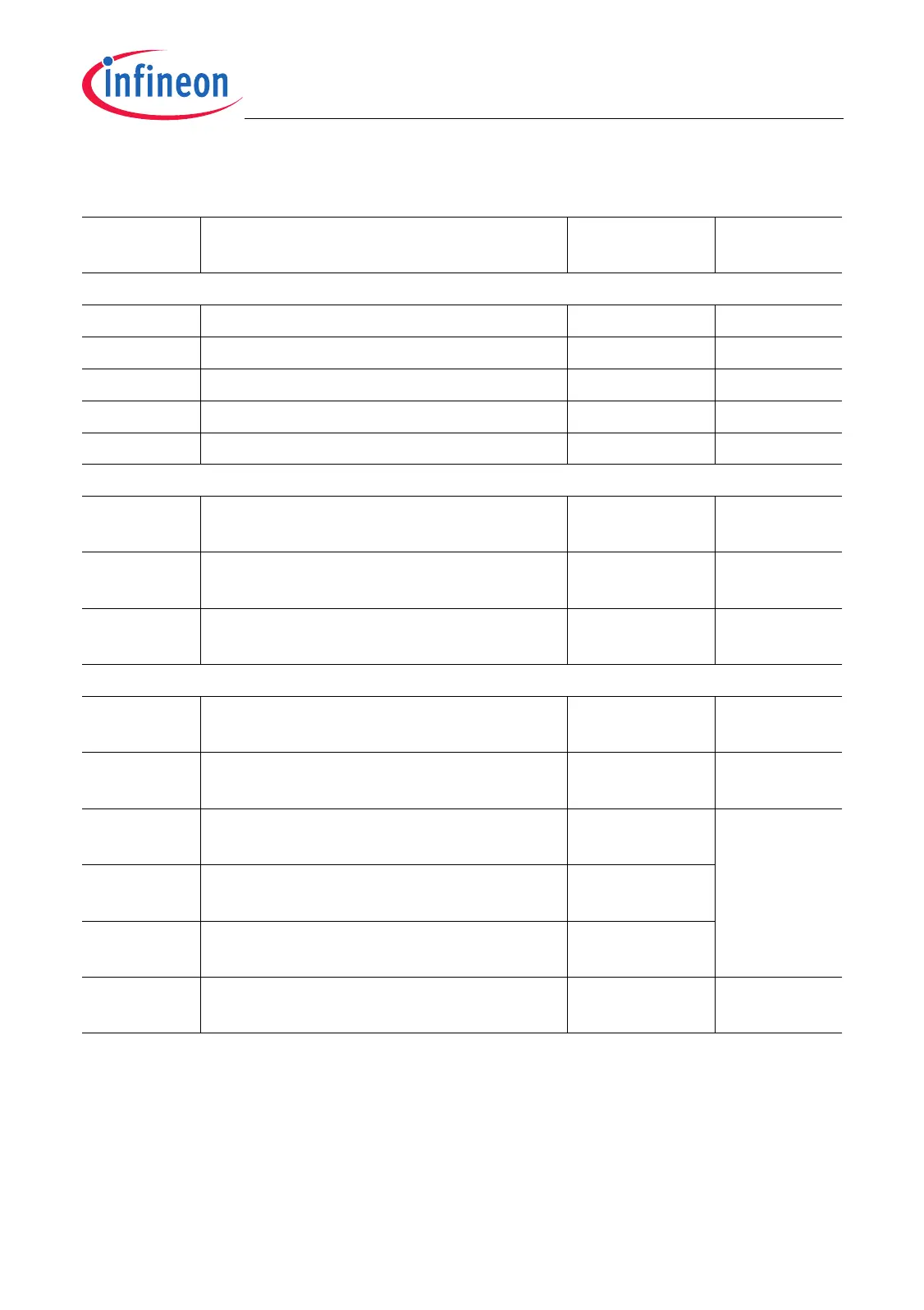

Table 26-8 Registers Overview - FADC Kernel Registers

Register

Short Name

Register Long Name Offset

Address

Description

see

Global Registers

ID Module Identification Register 08

H

Page 26-29

CRSR Conversion Request Status Register 10

H

Page 26-30

FMR Flag Modification Register 14

H

Page 26-32

NCTR Neighbor Channel Trigger Register 18

H

Page 26-34

GCR Global Control Register 1C

H

Page 26-37

Channel Registers

CFGRx Channel x Configuration Register

(x = 0-1)

20

H

+ (x × 4) Page 26-41

ACRx Channel x Analog Control Register

(x = 0-1)

30

H

+ (x × 4) Page 26-45

RCHx Channel x Conversion Result Register

(x = 0-1)

40

H

+ (x × 4) Page 26-47

Filter Registers

FCRn Filter n Control Register

(n = 0-1)

60

H

+ (n × 20

H

) Page 26-48

CRRn Filter n Current Result Register

(n = 0-1)

64

H

+ (n × 20

H

) Page 26-51

Page 26-52

IRR1n Filter n Intermediate Result Register 1

(n = 0-1)

68

H

+ (n × 20

H

) Page 26-54

IRR2n Filter n Intermediate Result Register 2

(n = 0)

6C

H

+ (n × 20

H

)

IRR3n Filter n Intermediate Result Register 3

(n = 0)

70

H

+ (n × 20

H

)

FRRn Filter n Final Result Register

(n = 0-1)

74

H

+ (n × 20

H

) Page 26-55

Loading...

Loading...