TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-76 V2.0, 2007-07

MLI, V2.0

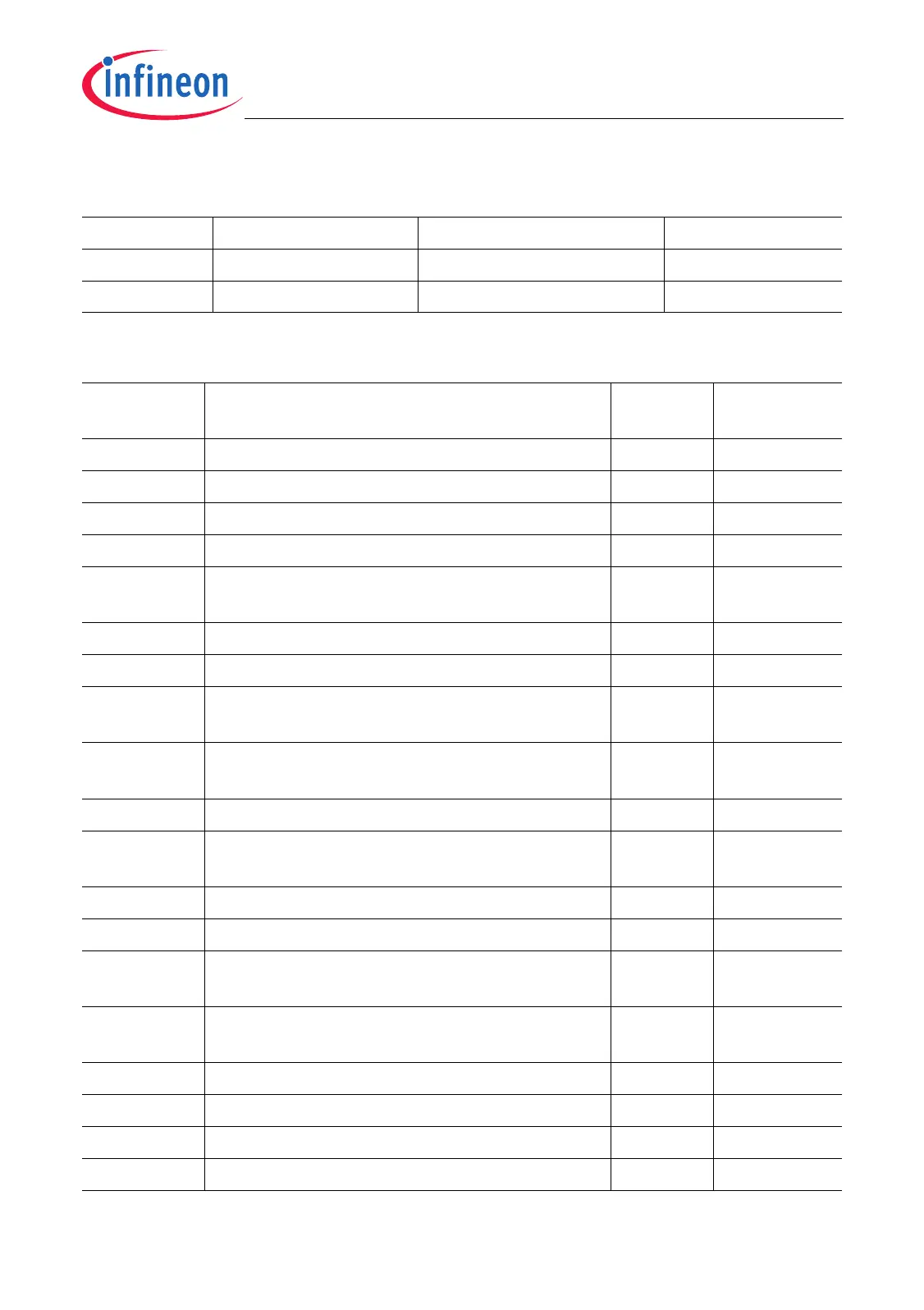

Table 23-9 Registers Address Space - MLI Registers

Module Base Address End Address Note

MLI0 F010 C000

H

F010 C0FF

H

–

MLI1 F010 C100

H

F010 C1FF

H

–

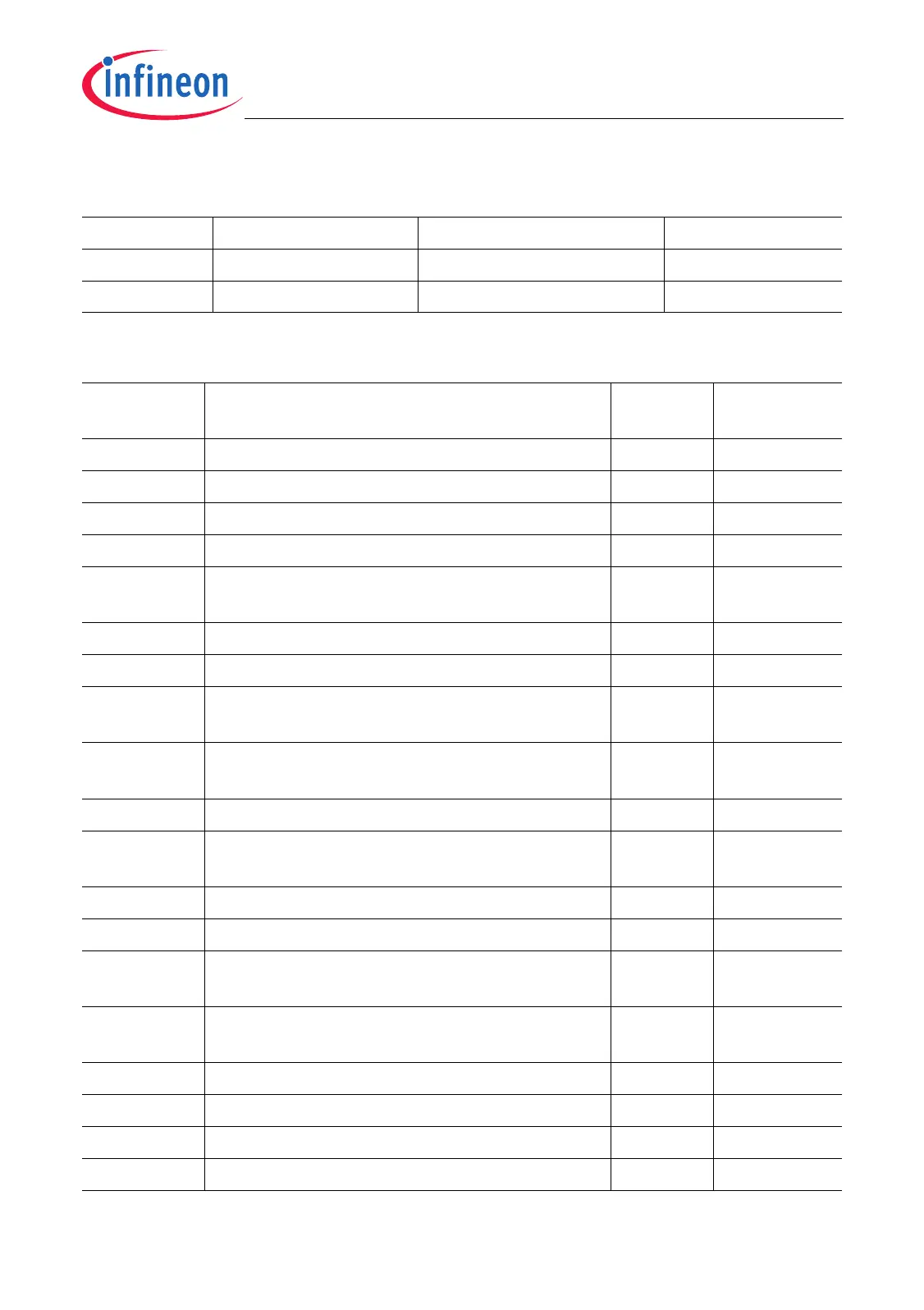

Table 23-10 Registers Overview - MLI Kernel Registers

Register

Short Name

Register Long Name Offset

Address

Description

see

ID Module Identification Register 08

H

Page 23-78

FDR Fractional Divider Register 0C

H

Page 23-79

TCR Transmitter Control Register 10

H

Page 23-90

TSTATR Transmitter Status Register 14

H

Page 23-93

TPxSTATR Transmitter Pipe x Status Register 18

H

+

(x * 4)

Page 23-95

TCMDR Transmitter Command Register 28

H

Page 23-97

TRSTATR Transmitter Receiver Status Register 2C

H

Page 23-99

TPxAOFR Transmitter Pipe x Address Offset Register 30

H

+

(x * 4)

Page 23-103

TPxDATAR Transmitter Pipe x Data Register 40

H

+

(x * 4)

Page 23-101

TDRAR Transmitter Data Read Answer Register 50

H

Page 23-101

TPxBAR Transmitter Pipe x Base Address Register 54

H

+

(x * 4)

Page 23-102

TCBAR Transmitter Copy Base Address Register 64

H

Page 23-104

RCR Receiver Control Register 68

H

Page 23-110

RPxBAR Receiver Pipe x Base Address Register 6C

H

+

(x * 4)

Page 23-115

RPxSTATR Receiver Pipe x Status Register 7C

H

+

(x * 4)

Page 23-113

RADDR Receiver Address Register 8C

H

Page 23-116

RDATAR Receiver Data Register 90

H

Page 23-114

SCR Set Clear Register 94

H

Page 23-81

TIER Transmitter Interrupt Enable Register 98

H

Page 23-105

Loading...

Loading...