TC1796

Peripheral Units (Vol. 2 of 2)

Analog-to-Digital Converter (ADC)

User’s Manual 25-58 V2.0, 2007-07

ADC, V2.0

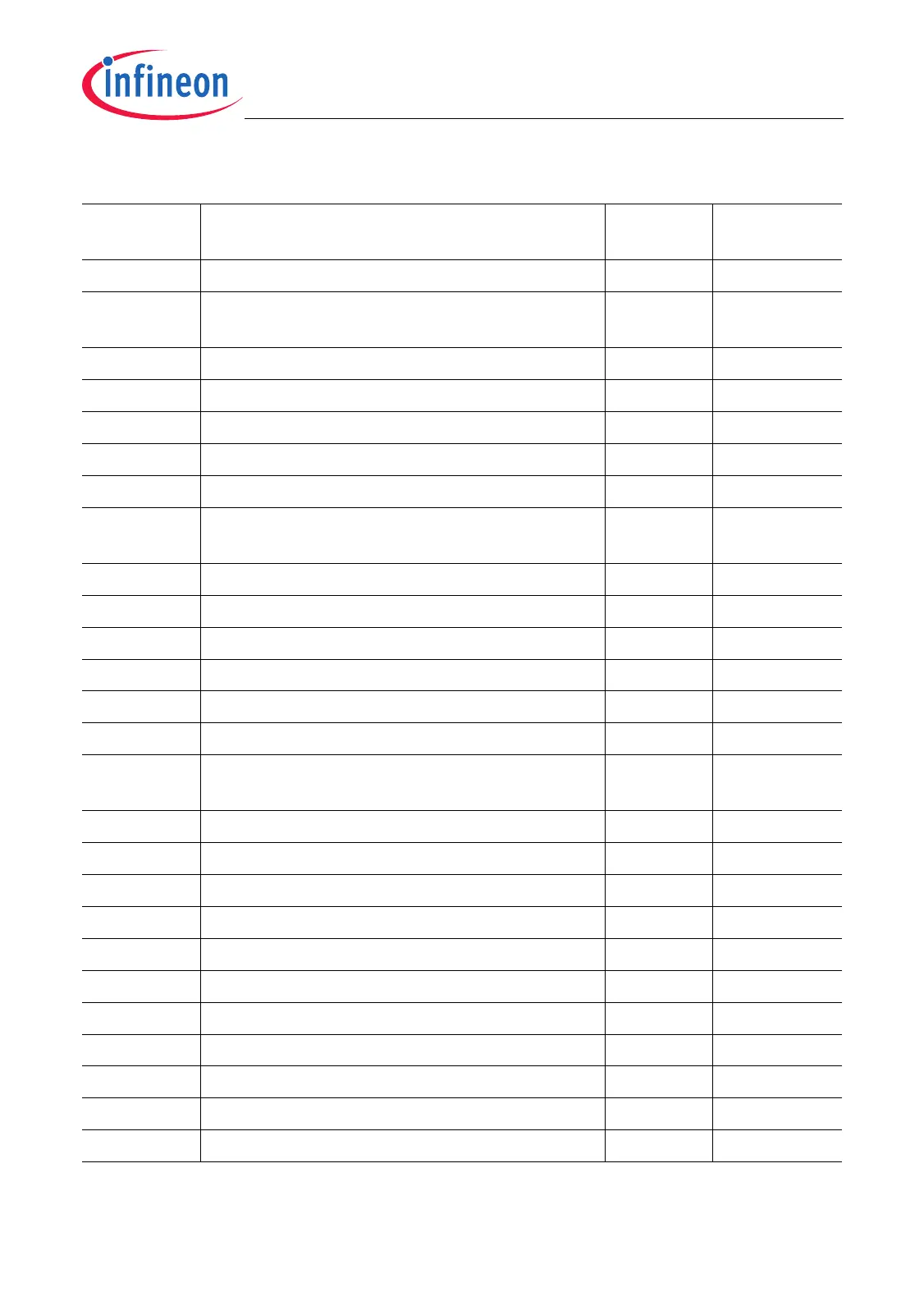

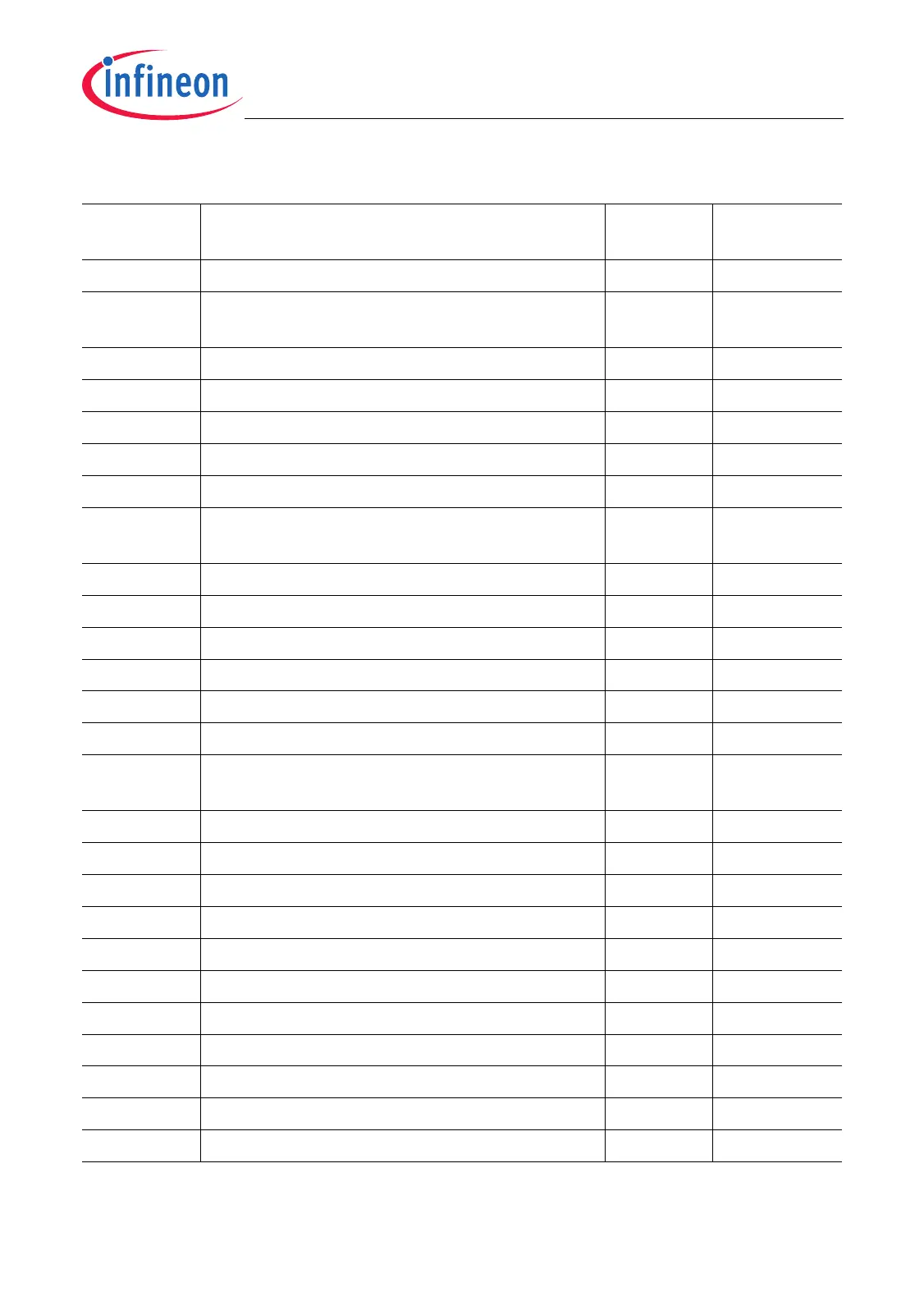

Table 25-13 Registers Overview - ADC Kernel Registers

Register

Short Name

Register Long Name Offset

Address

1)

1) The absolute register address is calculated as follows:

Module Base Address (Table 25-12) + Offset Address (shown in this column)

Description

see

ID Module Identification Register 008

H

Page 25-59

CHCONm Channel Control Register m (m = 0-15) 010

H

+

n × 4

H

Page 25-60

AP Arbitration Participation Register 084

H

Page 25-78

SAL Source Arbitration Level Register 088

H

Page 25-79

TTC Timer Trigger Control Register 08C

H

Page 25-65

EXTC External Trigger Control Register 090

H

Page 25-73

SCON Source Control Register 098

H

Page 25-81

LCCONx Limit Check Control Register x (x = 0-3) 100

H

+

m × 4

H

Page 25-80

TCON Timer Control Register 114

H

Page 25-66

CHIN Channel Injection Control Register 118

H

Page 25-90

QR Queue Register 11C

H

Page 25-71

CON Converter Control Register 120

H

Page 25-82

SCN Auto Scan Control Register 124

H

Page 25-75

REQ0 Conversion Request Register SW0 128

H

Page 25-92

CHSTATm Channel Status Register m (m = 0-15) 130

H

+

n × 4

H

Page 25-63

QUEUE0 Queue Status Register 170

H

Page 25-69

SW0CRP Software SW0 Conv. Req. Pending Reg. 180

H

Page 25-93

ASCRP Auto Scan Conversion Req. Pending Reg. 188

H

Page 25-77

SYSTAT Sychronization Status Register 190

H

Page 25-84

TSTAT Timer Status Register 1B0

H

Page 25-67

STAT Converter Status Register 1B4

H

Page 25-86

TCRP Timer Conversion Req. Pending Register 1B8

H

Page 25-68

EXCRP External Conversion Req. Pending Register 1BC

H

Page 25-74

MSS0 Module Service Request Status Register 0 1D0

H

Page 25-94

MSS1 Module Service Request Status Register 1 1D4

H

Page 25-95

SRNP Service Request Node Pointer Register 1DC

H

Page 25-97

Loading...

Loading...