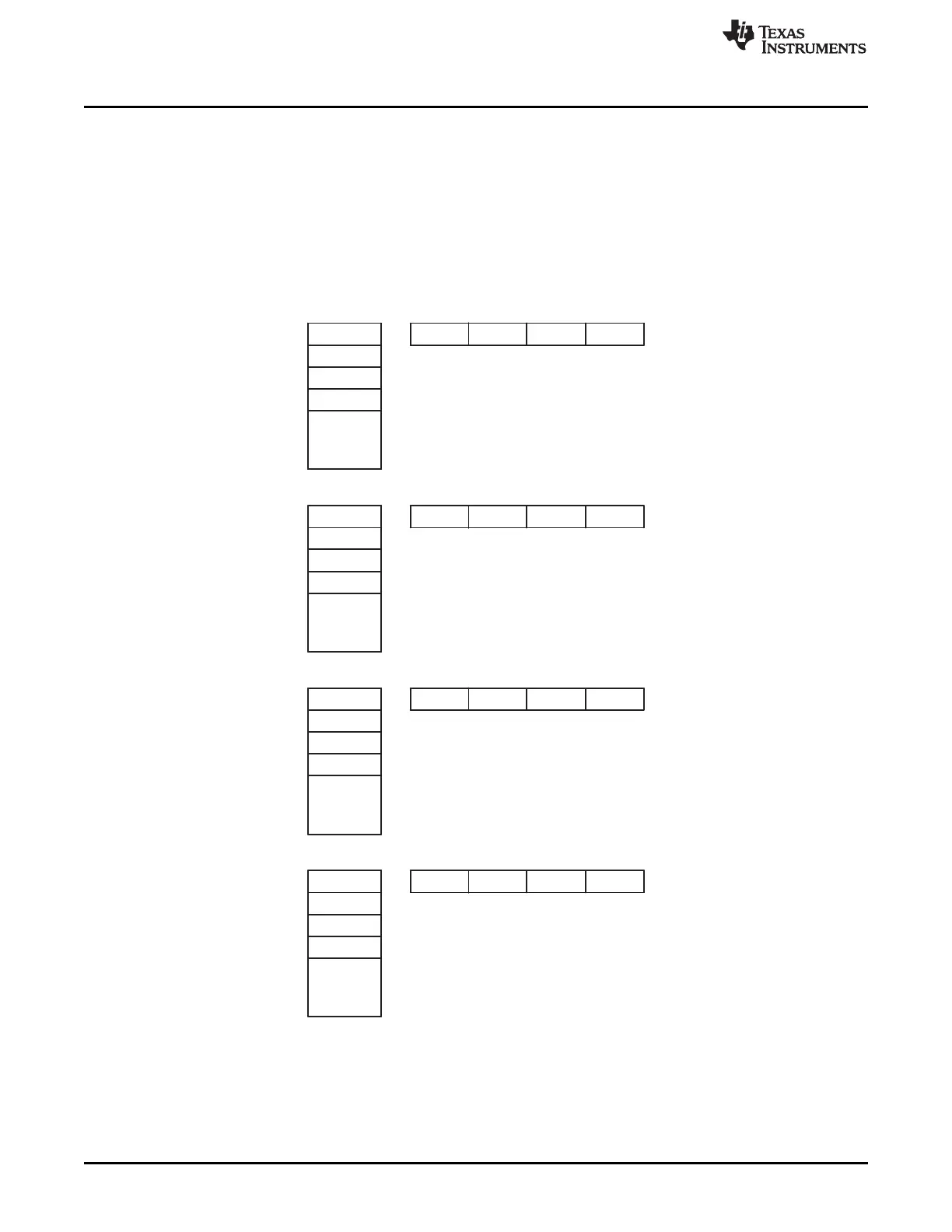

1st

2nd

3rd

4th

3

4th 3rd 2nd 1st

Support byten = ”1111”

Support byten = ”0111”

3rd

2nd

1st

3

3rd 2nd 1st

Support byten = ”0011”

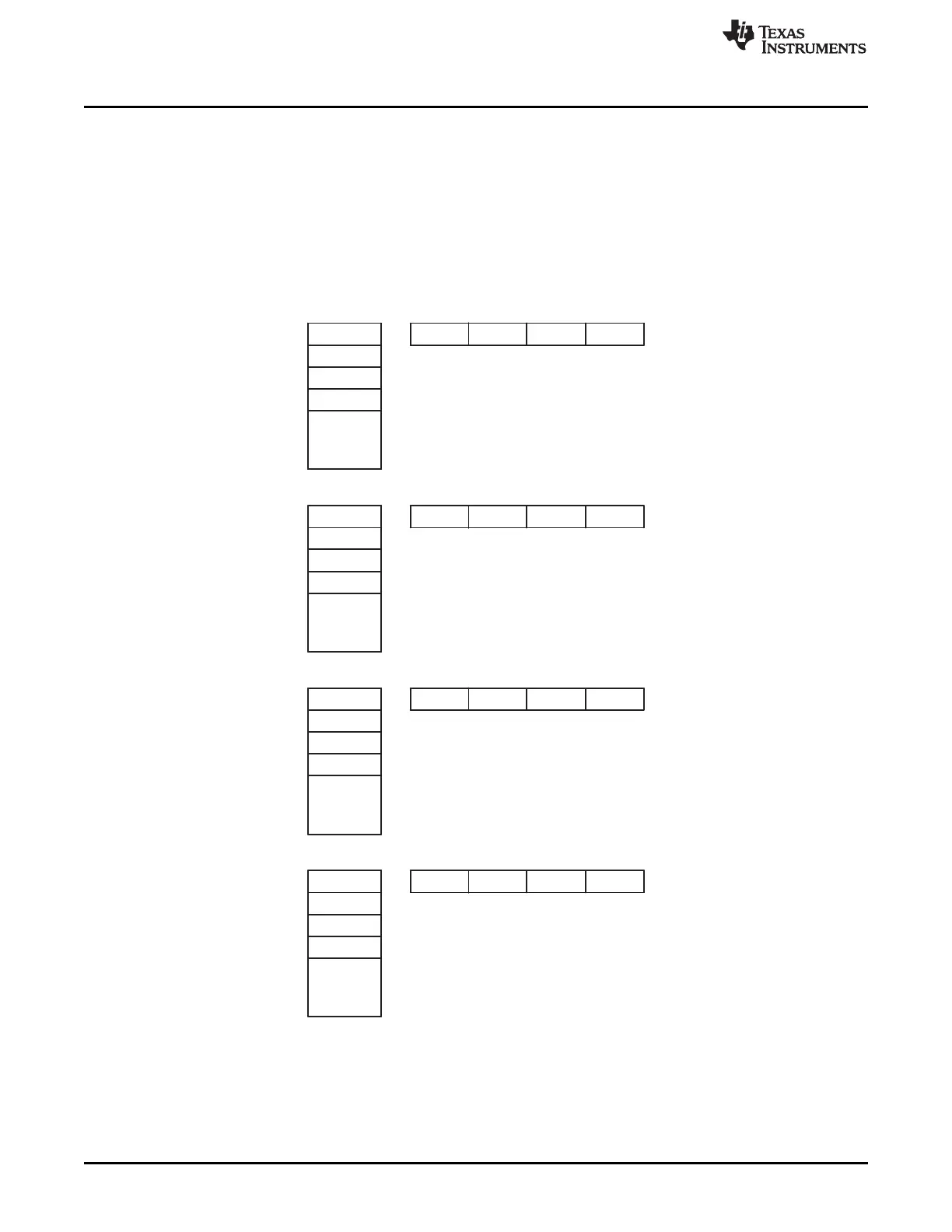

1st

2nd

3

2nd 1st

0

Support byten = ”0001”

1st

3

1st

0

0

0

FIFO MMCDRR or MMCDXR registers

Architecture

www.ti.com

1102

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Multimedia Card (MMC)/Secure Digital (SD) Card Controller

25.2.5 Data Flow in the Data Registers (MMCDRR and MMCDXR)

The CPU or EDMA controller can read 32 bits at a time from the FIFO by reading the MMC data receive

register (MMCDRR) and write 32 bits at a time to the FIFO by writing to the MMC data transmit register

(MMCDXR). However, since the memory card is an 8-bit device, it transmits or receives one byte at a

time. Figure 25-8 shows how the data size is handled by the data registers in little-endian mode.

Figure 25-8. Little-Endian Access to MMCDXR/MMCDRR from the CPU or the EDMA

Loading...

Loading...