Registers

www.ti.com

540

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

16.4.2.6.6 Interrupt Evaluate Register (IEVAL)

The interrupt evaluate register (IEVAL) is the only register that physically exists in both the global region

and the shadow regions. In other words, the read/write accessibility for the shadow region IEVAL is not

affected by the DMA/QDMA region access registers (DRAEm and QRAEm). IEVAL is needed for robust

ISR operations to ensure that interrupts are not missed by the CPU.

The IEVAL is shown in Figure 16-75 and described in Table 16-54.

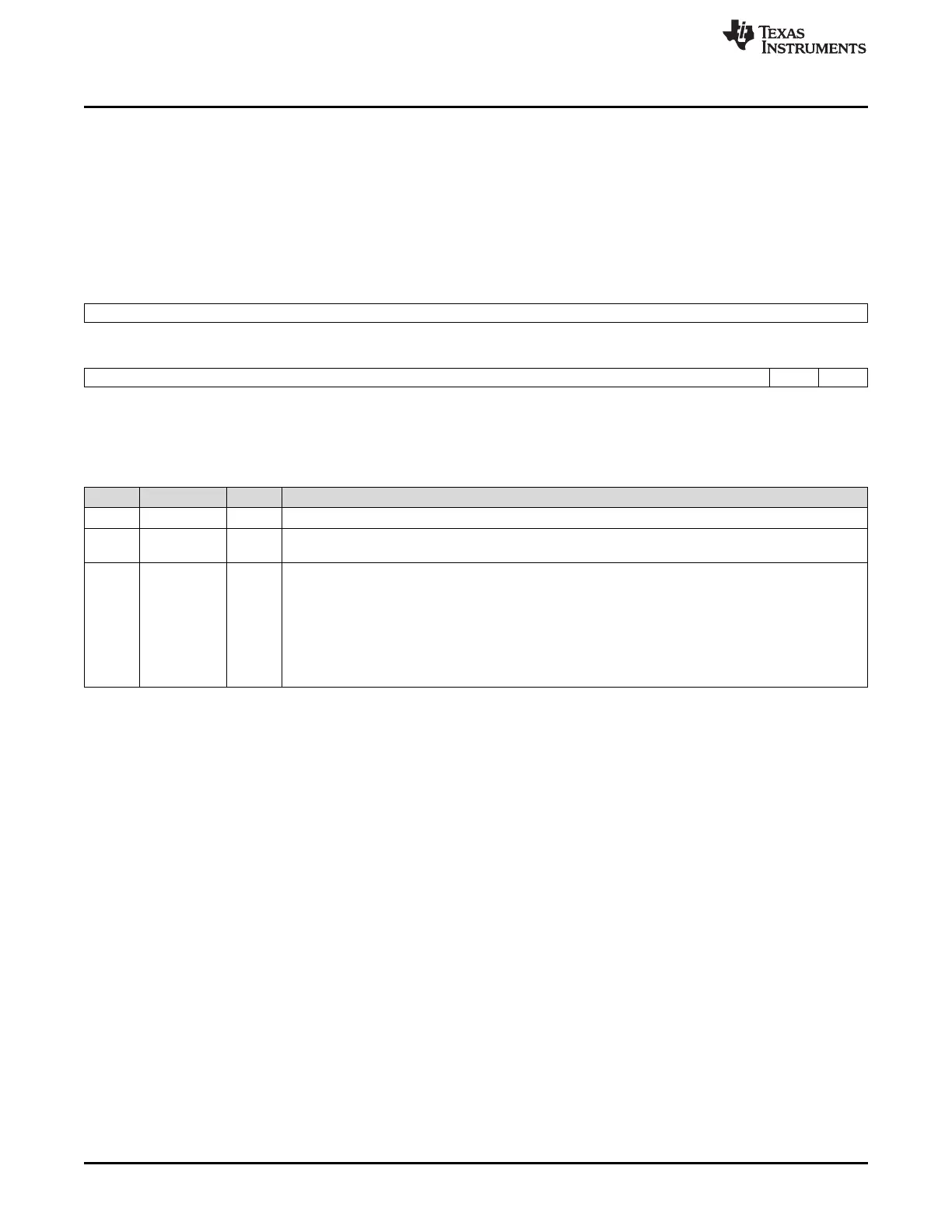

Figure 16-75. Interrupt Evaluate Register (IEVAL)

31 16

Reserved

R-0

15 2 1 0

Reserved Rsvd EVAL

R-0 W-0 W-0

LEGEND: R = Read only; W = Write only; -n = value after reset

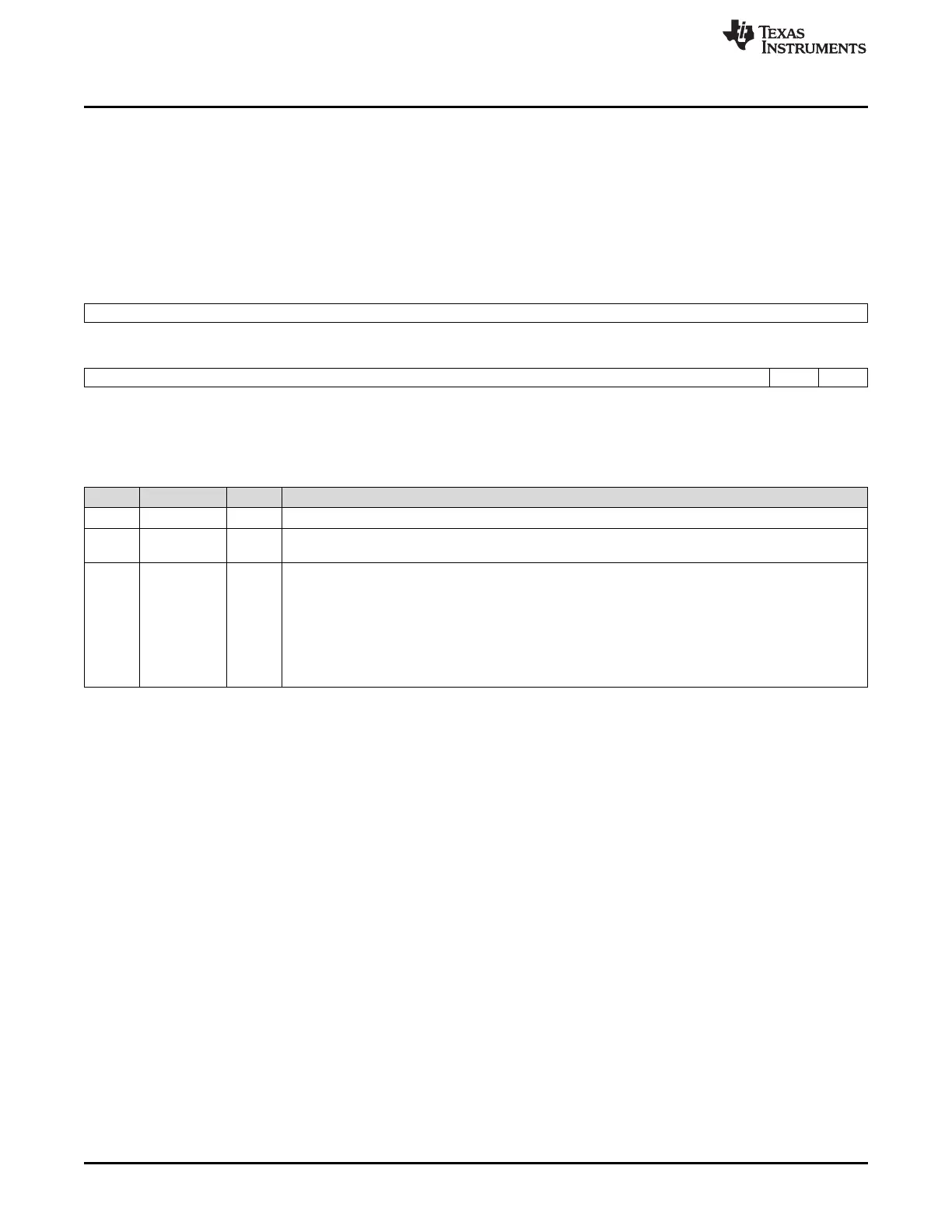

Table 16-54. Interrupt Evaluate Register (IEVAL) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved

1 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

0 EVAL Interrupt evaluate.

0 No effect.

1 Causes EDMA3CC completion interrupt to be pulsed, if any enabled (IERn = 1) interrupts are still

pending (IPRn = 1).

The EDMA3CC completion region interrupt that is pulsed depends on which IEVAL is being exercised.

For example, writing to the EVAL bit in IEVAL0 pulses the region 0 completion interrupt, but writing to

the EVAL bit in IEVAL1 pulses the region 1 completion interrupt.

Loading...

Loading...