Registers

www.ti.com

930

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Inter-Integrated Circuit (I2C) Module

22.3.21 I2C Pin Data Clear Register (ICPDCLR)

The I2C pin data clear register (ICPDCLR) is an alias of the I2C pin data out register (ICPDOUT). Writing

a 1 to a bit in ICPDCLR clears the corresponding bit in ICPDOUT to a 0, while writing a 0 keeps the bit

unchanged. ICPDCLR is shown in Figure 22-35 and described in Table 22-28.

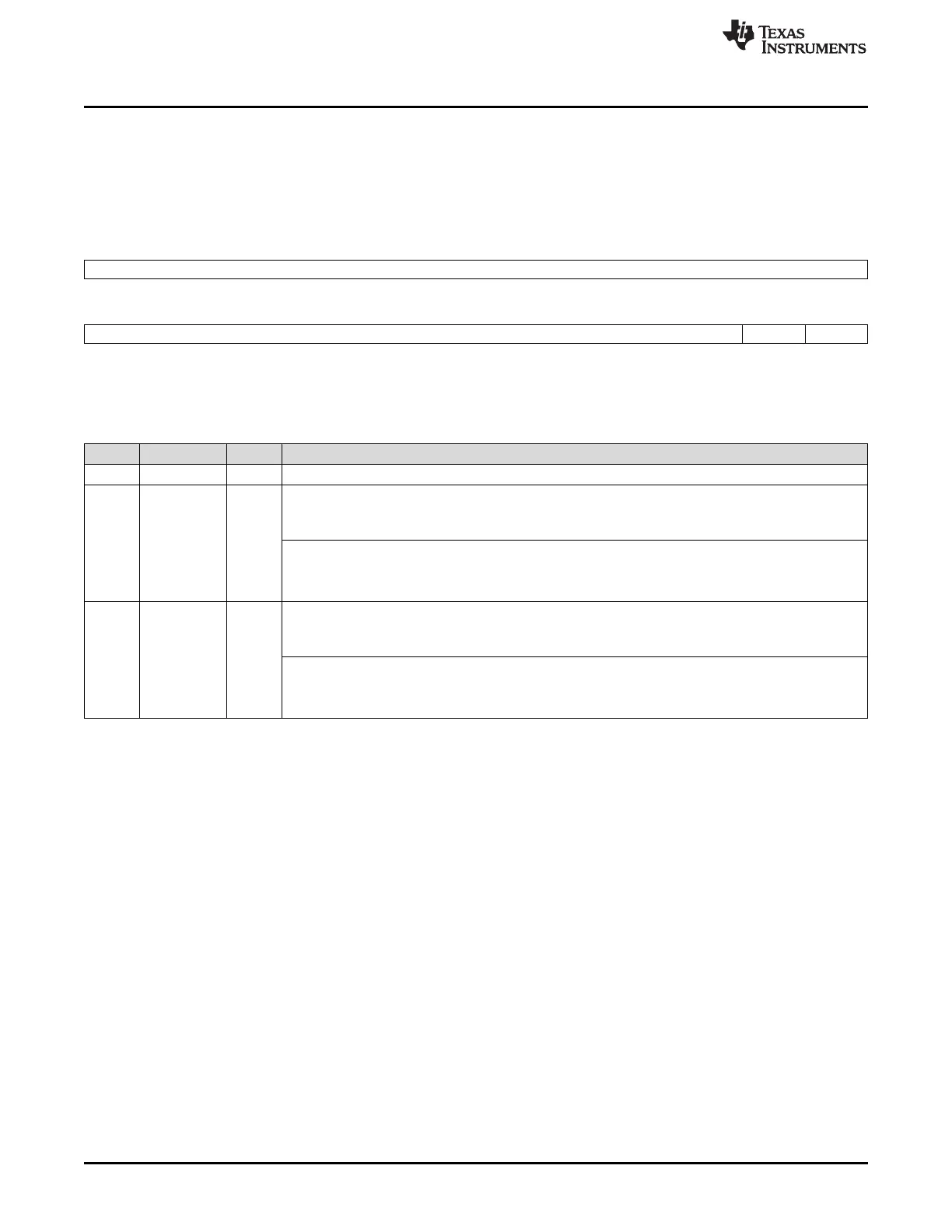

Figure 22-35. I2C Pin Data Clear Register (ICPDCLR)

31 16

Reserved

R-0

15 2 1 0

Reserved PDCLR1 PDCLR0

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

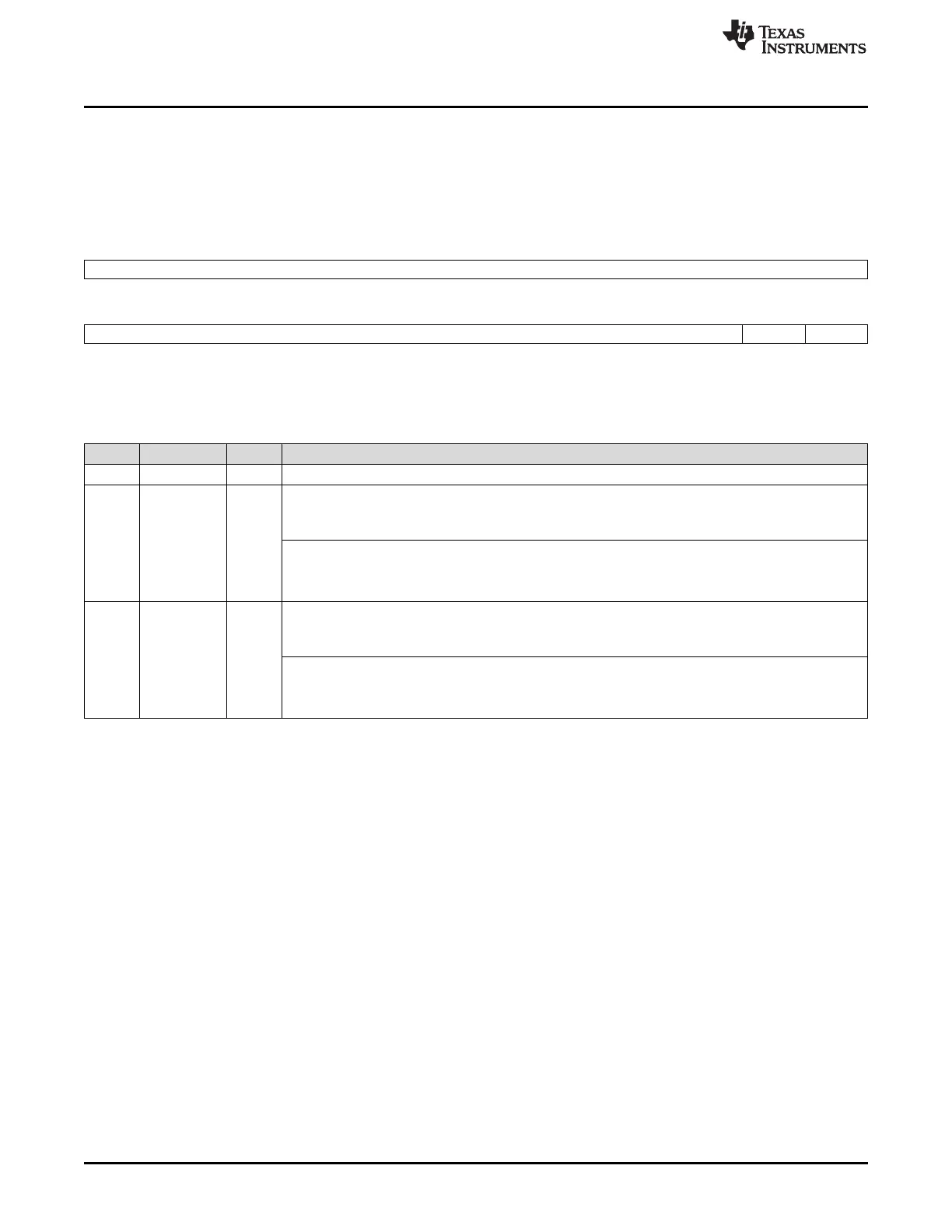

Table 22-28. I2C Pin Data Clear Register (ICPDCLR) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 These reserved bit locations are always read as zeros. A value written to this field has no effect.

1 PDCLR1 Used to clear the PDOUT1 bit in the I2C pin data out register (ICPDOUT) that corresponds to the

I2Cx_SDA GPIO pin.

During reads: Reads return indeterminate values.

During writes:

0 No effect

1 PDOUT1 bit is cleared to logic low.

0 PDCLR0 Used to clear the PDOUT0 bit in the I2C pin data out register (ICPDOUT) that corresponds to the

I2Cx_SCL GPIO pin.

During reads: Reads return indeterminate values.

During writes:

0 No effect

1 PDOUT0 bit is cleared to logic low.

Loading...

Loading...