Registers

www.ti.com

550

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

16.4.3.4 Error Registers

16.4.3.4.1 Error Status Register (ERRSTAT)

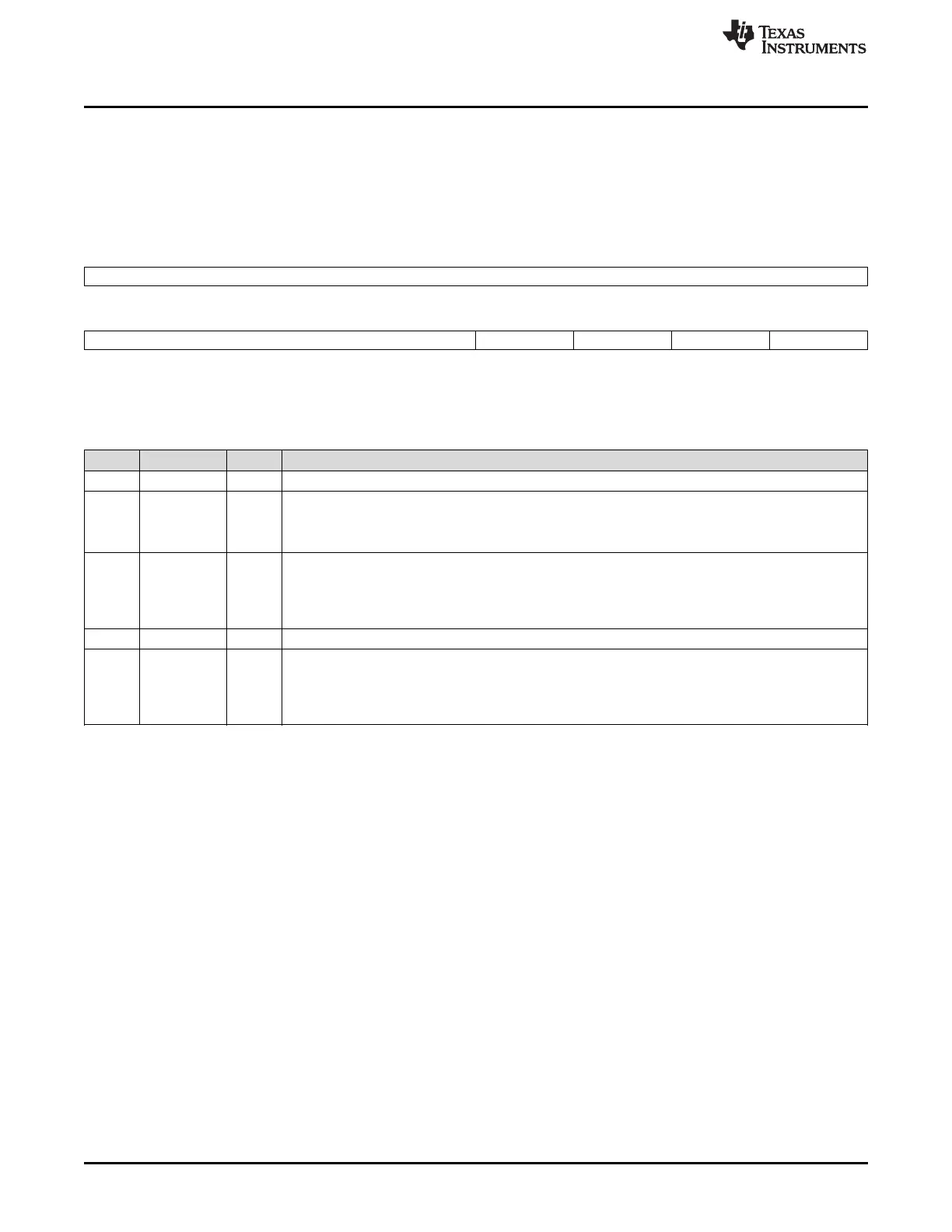

The error status register (ERRSTAT) is shown in Figure 16-85 and described in Table 16-65.

Figure 16-85. Error Status Register (ERRSTAT)

31 16

Reserved

R-0

15 4 3 2 1 0

Reserved MMRAERR TRERR Reserved BUSERR

R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

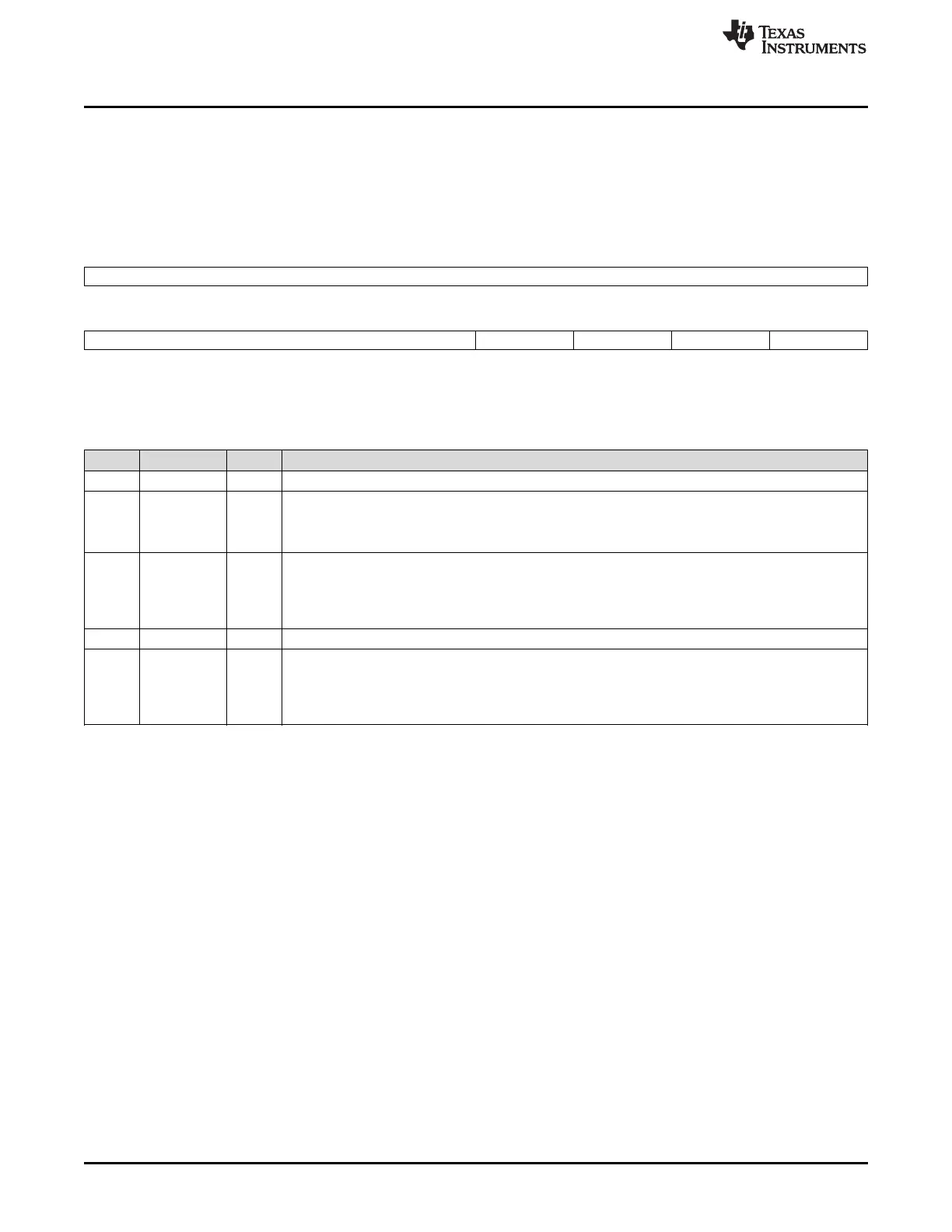

Table 16-65. Error Status Register (ERRSTAT) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reserved

3 MMRAERR MMR address error.

0 MMR address error is not detected.

1 User attempted to read or write to an invalid address in configuration memory map.

2 TRERR Transfer request (TR) error event.

0 Transfer request (TR) error is not detected.

1 Transfer request (TR) detected that violates constant addressing mode transfer (SAM or DAM is set to

1) alignment rules or has ACNT or BCNT == 0.

1 Reserved 0 Reserved

0 BUSERR Bus error event.

0 Bus error is not detected.

1 EDMA3TC has detected an error at source or destination address. Error information can be read from

the error details register (ERRDET).

Loading...

Loading...