Registers

www.ti.com

952

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Liquid Crystal Display Controller (LCDC)

23.3.3 LCD Status Register (LCD_STAT)

The LCD status register (LCD_STAT) contains bits that signal status and error conditions to the

processor. Each of the LCD status bits signals an interrupt request as long as the bit is set AND the

interrupt enable for that bit is also set (see the LCD raster control and LCD DMA control registers for these

enables). Writing a 1 to each bit clears it; once the bit is cleared, the interrupt is cleared. The LCD_STAT

is shown in Figure 23-17 and described in Table 23-13.

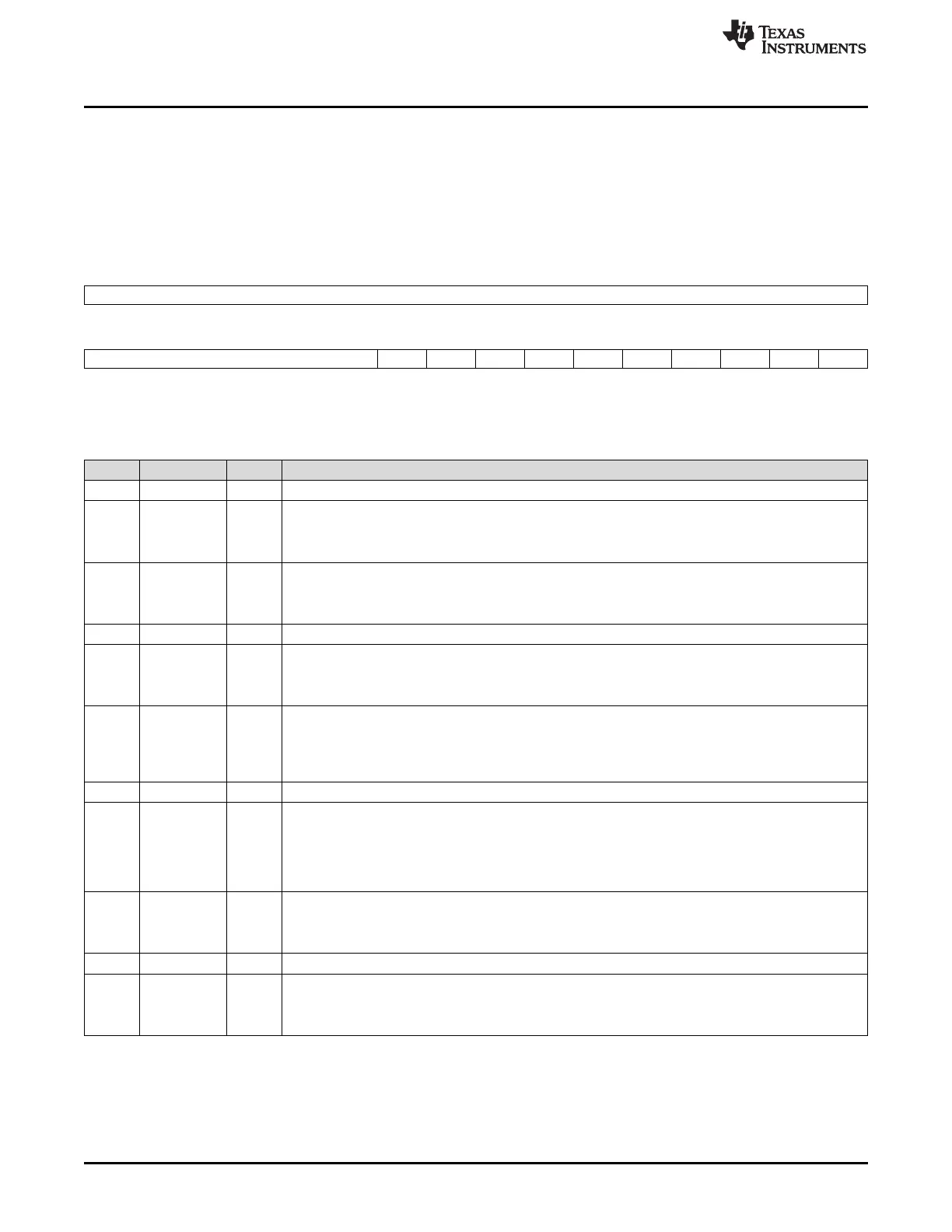

Figure 23-17. LCD Status Register (LCD_STAT)

31 16

Reserved

R-0

15 10 9 8 7 6 5 4 3 2 1 0

Reserved EOF1 EOF0 Rsvd PL FUF Rsvd ABC SYNC Rsvd DONE

R-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R = Read only; -n = value after reset

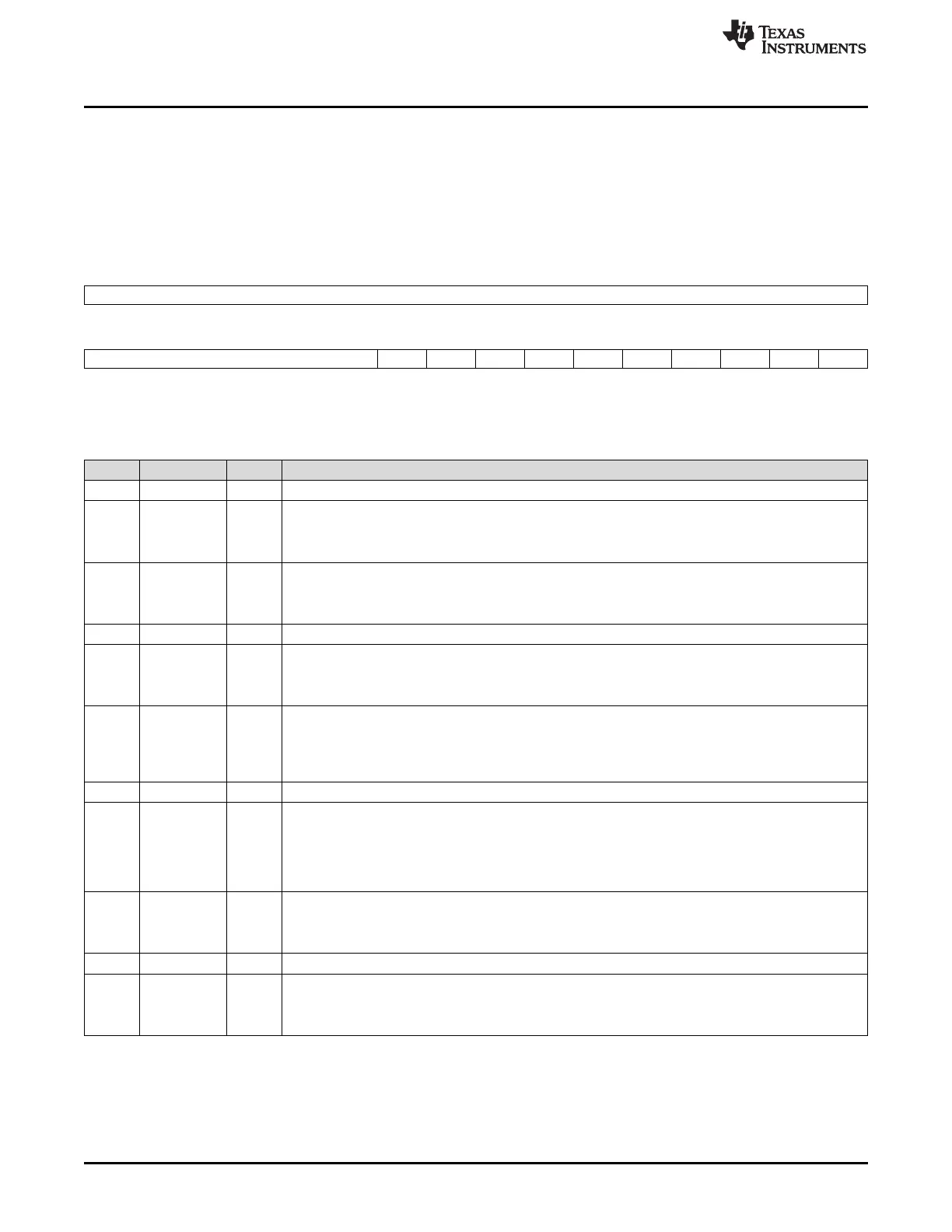

Table 23-13. LCD Status Register (LCD_STAT) Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reserved

9 EOF1 End of Frame 1

0 no end of frame 1 detected

1 end of frame 1 detected

8 EOF0 End of Frame 0

0 no end of frame 0 detected

1 end of frame 0 detected

7 Reserved 0 Reserved

6 PL Loaded Palette

0 The palette is not loaded

1 The palette is loaded

5 FUF FIFO Underflow Status

0 FIFO has not underrun

1 LCD dither logic not supplying data to FIFO at a sufficient rate, FIFO has completely emptied and data

pin driver logic has attempted to take added data from FIFO

4 Reserved 0 Reserved

3 ABC AC Bias Count Status

0 AC bias transition counter has not decremented to zero

1 AC bias transition counter has decremented to zero, indicating that the LCD_AC_O line has transitioned

the number of times that is specified by the ACB_I control bit field. Counter is reloaded with value in

ACB_I but is disabled until the user clears ABC.

2 SYNC Sync Lost

0 normal

1 Frame Synchronization Lost has occurred

1 Reserved 0 Reserved

0 DONE Raster or LIDD Frame Done (shared; depends on whether Raster or LIDD mode enabled)

0 Raster or DMA_to_LIDD engine is enabled

1 Raster or DMA_to_LIDD disabled and the active frame has just completed

Loading...

Loading...