MPU Registers

www.ti.com

94

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Memory Protection Unit (MPU)

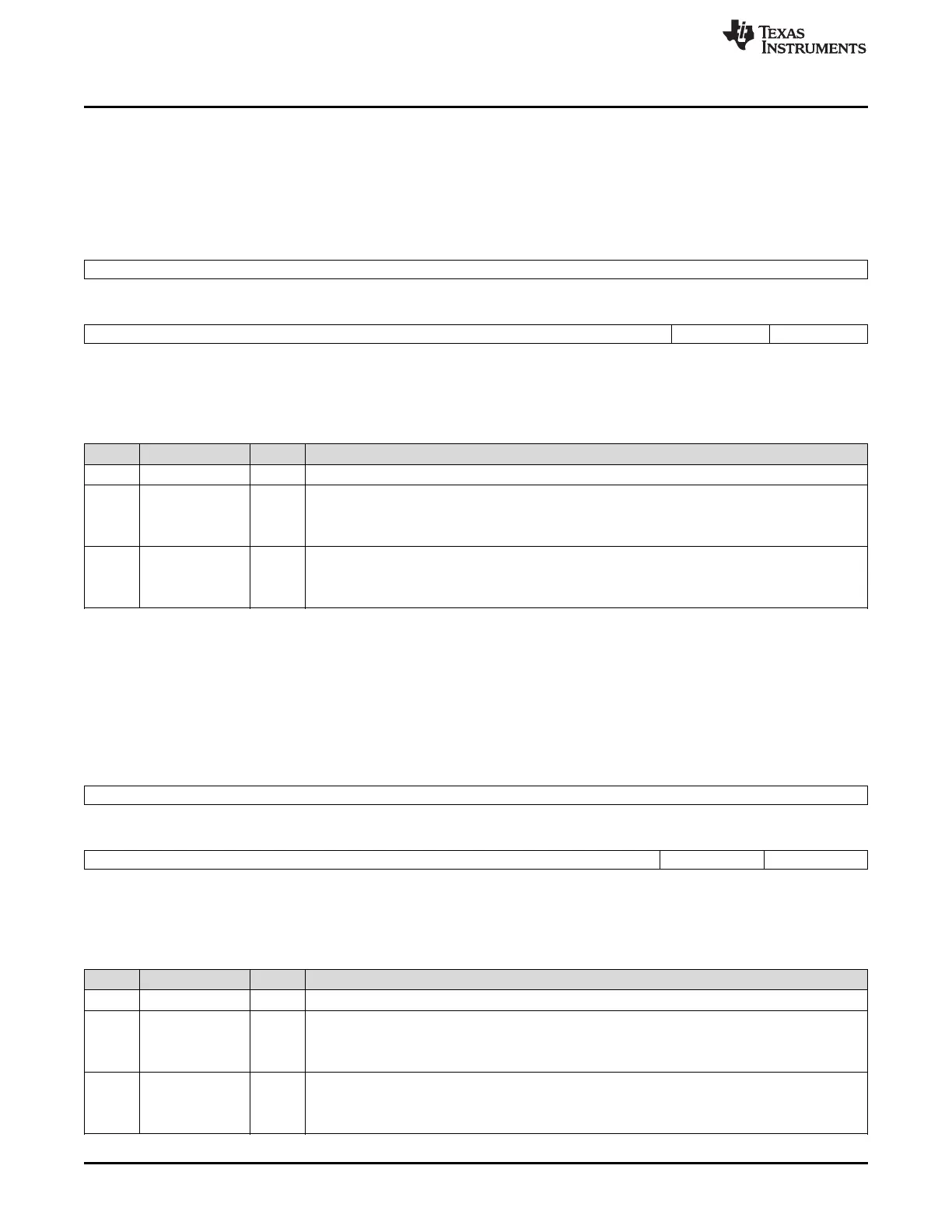

5.3.5 Interrupt Enable Set Register (IENSET)

Reading the interrupt enable set register (IENSET) returns the interrupts that are enabled. Software can

write to IENSET to enable an interrupt. Writes of 0 have no effect. The IENSET is shown in Figure 5-7 and

described in Table 5-12.

Figure 5-7. Interrupt Enable Set Register (IENSET)

31 16

Reserved

R-0

15 2 1 0

Reserved ADDRERR_EN PROTERR_EN

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 5-12. Interrupt Enable Set Register (IENSET) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved

1 ADDRERR_EN Address violation error enable.

0 Writing 0 has no effect.

1 Interrupt is enabled.

0 PROTERR_EN Protection violation error enable.

0 Writing 0 has no effect.

1 Interrupt is enabled.

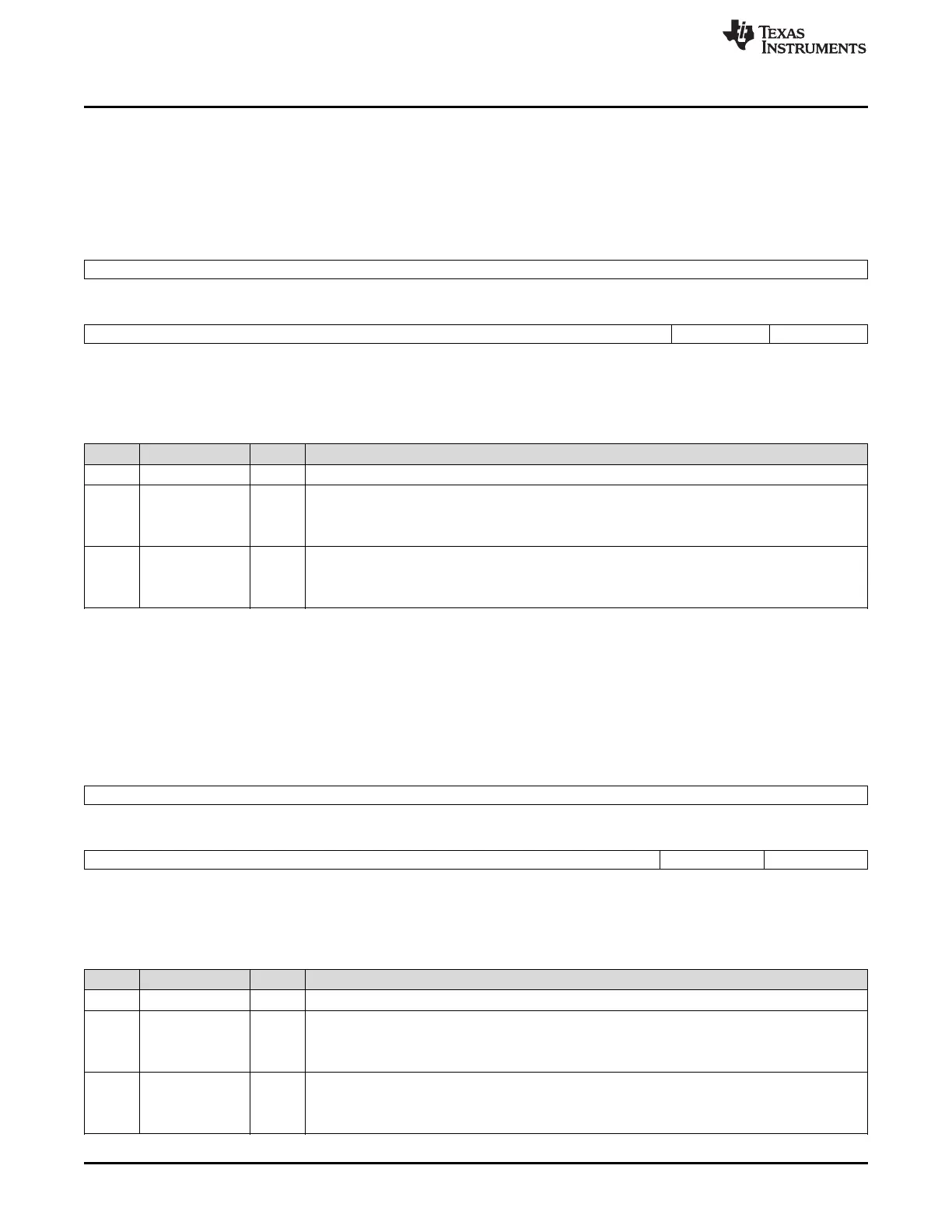

5.3.6 Interrupt Enable Clear Register (IENCLR)

Reading the interrupt enable clear register (IENCLR) returns the interrupts that are enabled. Software can

write to IENCLR to clear/disable an interrupt. Writes of 0 have no effect. The IENCLR is shown in

Figure 5-8 and described in Table 5-13.

Figure 5-8. Interrupt Enable Clear Register (IENCLR)

31 16

Reserved

R-0

15 2 1 0

Reserved ADDRERR_CLR PROTERR_CLR

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 5-13. Interrupt Enable Clear Register (IENCLR) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved

1 ADDRERR_CLR Address violation error disable.

0 Writing 0 has no effect.

1 Interrupt is cleared/disabled.

0 PROTERR_CLR Protection violation error disable.

0 Writing 0 has no effect.

1 Interrupt is cleared/disabled.

Loading...

Loading...