www.ti.com

Architecture

723

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface A (EMIFA)

18.2.5.6 NAND Flash Mode

NAND Flash Mode is a submode of both Normal Mode and Select Strobe Mode. Chip select EMA_CS[n]

(n = 2, 3, 4, or 5) may be placed in NAND Flash mode by setting the CSnNAND (n = 2, 3, 4, or 5) bit in

the NAND Flash control register (NANDFCR). Table 18-23 displays the bit fields present in NANDFCR

and briefly describes their use.

When a chip select space is configured to operate in NAND Flash mode, the EMIFA hardware can

calculate the error correction code (ECC) for each 518 byte data transfer to that chip select space. The

EMIFA hardware will not generate the NAND access cycle, which includes the command, address, and

data phases, necessary to complete a transfer to NAND Flash. All NAND Flash operations can be divided

into single asynchronous cycles, and with the help of software the EMIFA can execute a complete NAND

access cycle.

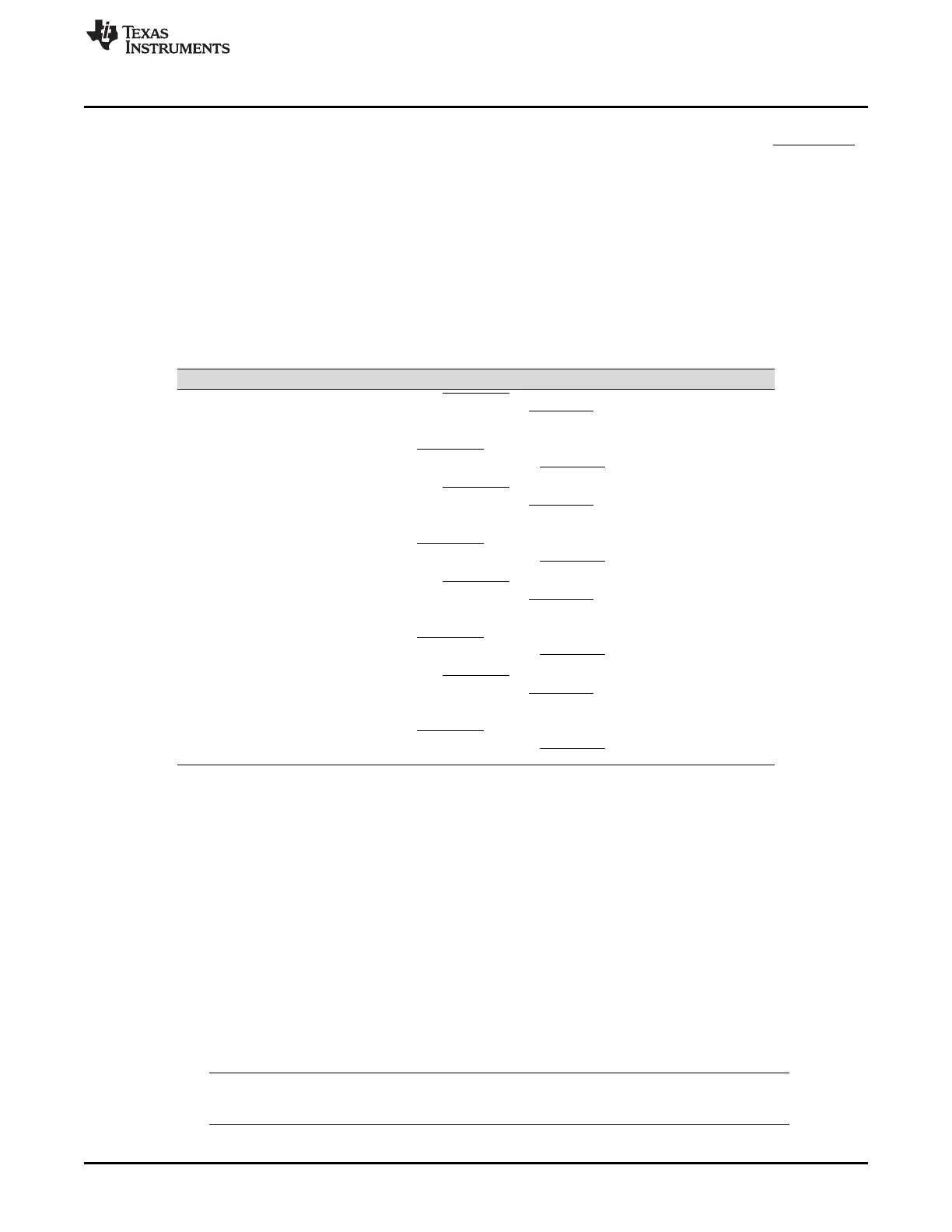

Table 18-23. Description of the NAND Flash Control Register (NANDFCR)

Parameter Description

CS5ECC NAND Flash ECC state for EMA_CS[5].

• Set to 1 to start an ECC calculation for EMA_CS[5]

• Cleared to 0 when NAND Flash 4 ECC register (NANDF4ECC) is read.

CS5NAND NAND Flash mode for EMA_CS[5].

• Set to 1 to enable NAND Flash mode for EMA_CS[5]

CS4ECC NAND Flash ECC state for EMA_CS[4].

• Set to 1 to start an ECC calculation for EMA_CS[4]

• Cleared to 0 when NAND Flash 3 ECC register (NANDF3ECC) is read.

CS4NAND NAND Flash mode for EMA_CS[4].

• Set to 1 to enable NAND Flash mode for EMA_CS[4]

CS3ECC NAND Flash ECC state for EMA_CS[3].

• Set to 1 to start an ECC calculation for EMA_CS[3]

• Cleared to 0 when NAND Flash 2ECC register (NANDF2ECC) is read.

CS3NAND NAND Flash mode for EMA_CS[3].

• Set to 1 to enable NAND Flash mode for EMA_CS[3]

CS2ECC NAND Flash ECC state for EMA_CS[2].

• Set to 1 to start an ECC calculation for EMA_CS[2]

• Cleared to 0 when NAND Flash 1 ECC register (NANDF1ECC) is read.

CS2NAND NAND Flash mode for EMA_CS[2].

• Set to 1 to enable NAND Flash mode for EMA_CS[2]

18.2.5.6.1 Configuring for NAND Flash Mode

Similar to the asynchronous accesses previously described, the EMIFA's memory-mapped registers must

be programmed appropriately to interface to a NAND Flash device. In addition to the fields listed in

Table 18-15, the CSnNAND (n = 2, 3, 4, or 5) bit of the NAND Flash control register (NANDFCR) should

be set to 1 to enter NAND Flash Mode. Note that the EW bit of CEnCFG should be cleared to avoid

enabling the wait feature while in NAND Flash Mode.

18.2.5.6.2 Connecting to NAND Flash

Figure 18-14 shows the EMIFA external pins used to interface with a NAND Flash device. EMIFA address

lines are used to drive the NAND Flash device's command latch enable (CLE) and address latch enable

(ALE) signals. Any EMIFA address lines may be used to drive the CLE and ALE signals of the NAND

Flash.

NOTE: The EMIFA will not control the NAND Flash device's write protect pin. The write protect pin

must be controlled outside of the EMIFA.

Loading...

Loading...