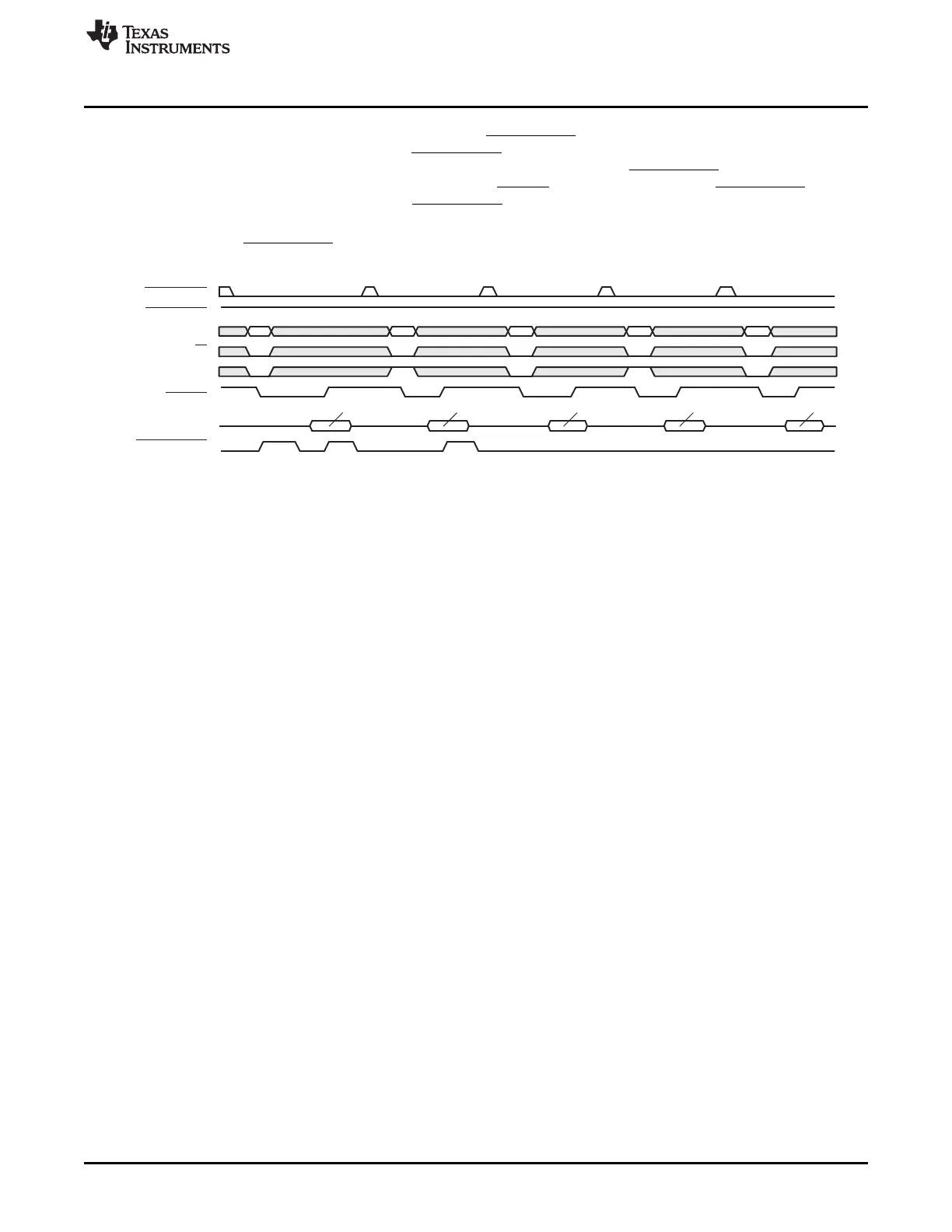

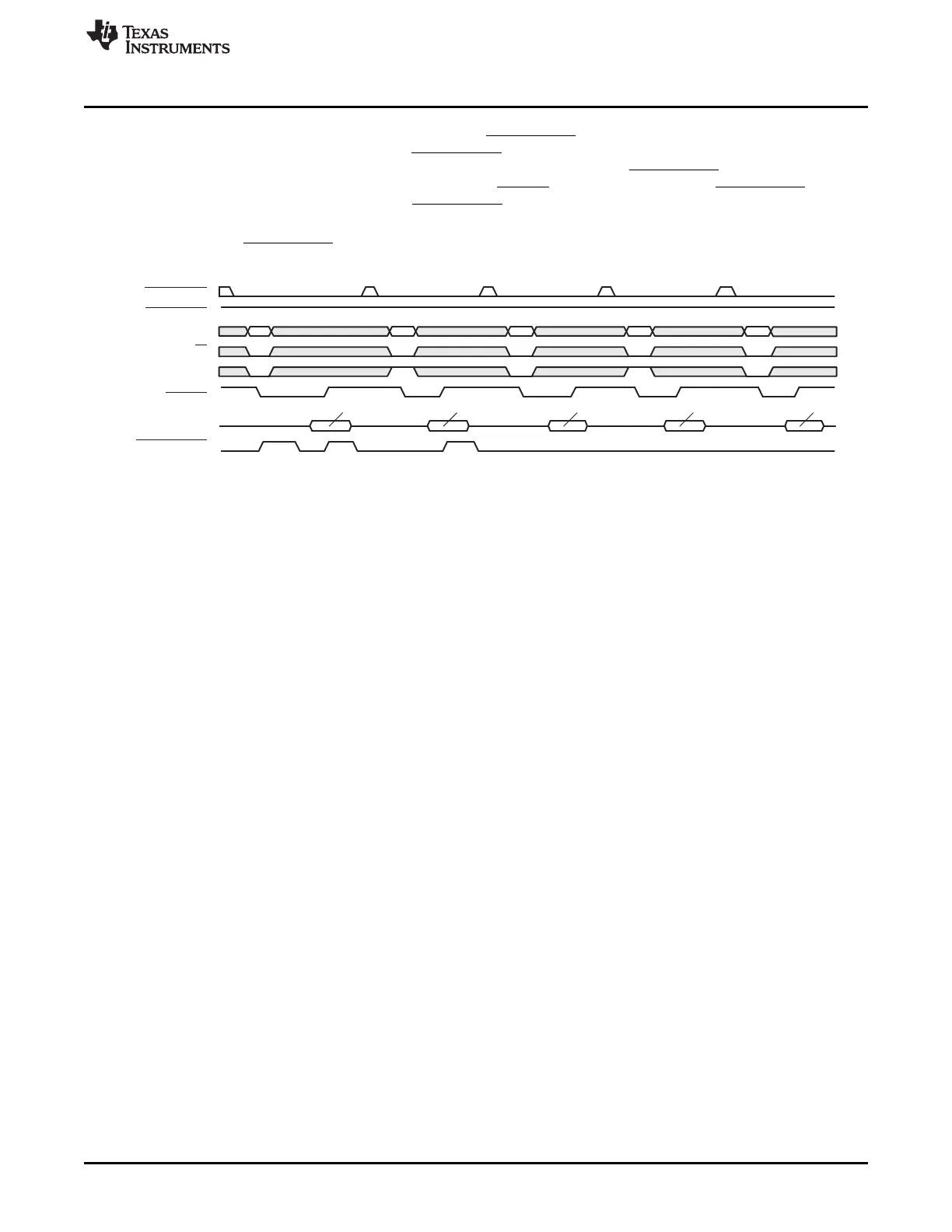

10 10 01 01 01

1st halfword2nd halfword1st halfword2nd halfword1st halfword

Internal

HSTRB

UHPI_HD[15:0]

UHPI_HRDY

UHPI_HHWIL

UHPI_HR/W

UHPI_HCNTL[1:0]

UHPI_HAS

UHPI_HCS

www.ti.com

Architecture

873

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Host Port Interface (HPI)

Figure 21-13 shows a case similar to that of Figure 21-12. However, in the case of Figure 21-13, the write

FIFO is not empty when the HPIA access is made. UHPI_HRDY goes high twice for the first halfword

access of the HPIA write cycle. The first UHPI_HRDY high period is due to the nonempty FIFO. The data

currently in the FIFO must first be written to the memory. This results in UHPI_HRDY going high

immediately after the falling edge of the data strobe (HSTRB). The second and third UHPI_HRDY high

periods occur for the writes to the HPIA. UHPI_HRDY remains low for the HPID accesses.

Figure 21-13. UHPI_HRDY Behavior During a Data Write Operation in the Multiplexed Mode

(Case 3: Autoincrementing Selected, FIFO Not Empty Before Write)

Loading...

Loading...