Registers

www.ti.com

660

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

EMAC/MDIO Module

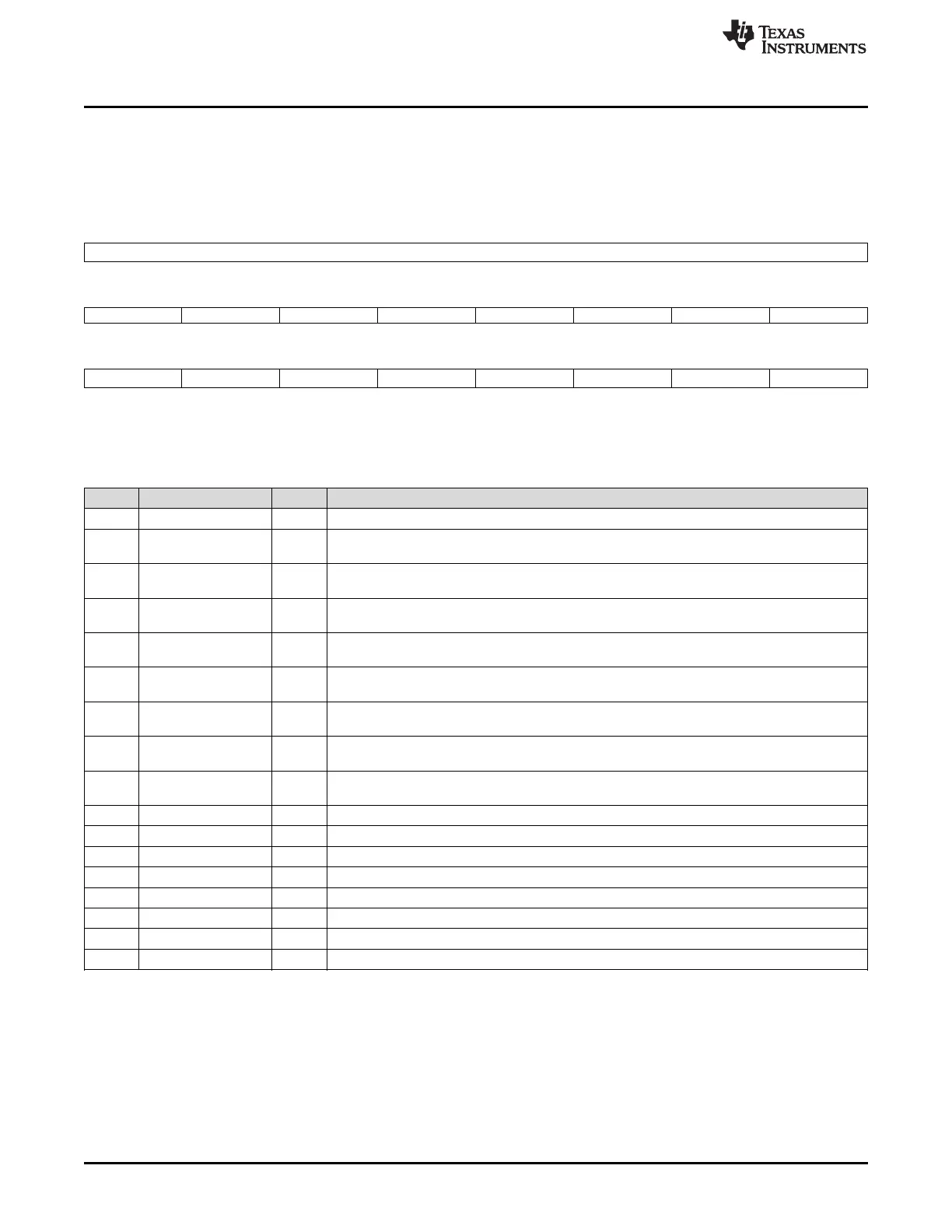

17.3.3.16 Receive Interrupt Mask Clear Register (RXINTMASKCLEAR)

The receive interrupt mask clear register (RXINTMASKCLEAR) is shown in Figure 17-54 and described in

Table 17-53.

Figure 17-54. Receive Interrupt Mask Clear Register (RXINTMASKCLEAR)

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

RX7THRESHMASK RX6THRESHMASK RX5THRESHMASK RX4THRESHMASK RX3THRESHMASK RX2THRESHMASK RX1THRESHMASK RX0THRESHMASK

R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0

7 6 5 4 3 2 1 0

RX7MASK RX6MASK RX5MASK RX4MASK RX3MASK RX2MASK RX1MASK RX0MASK

R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing a 0 has no effect); -n = value after reset

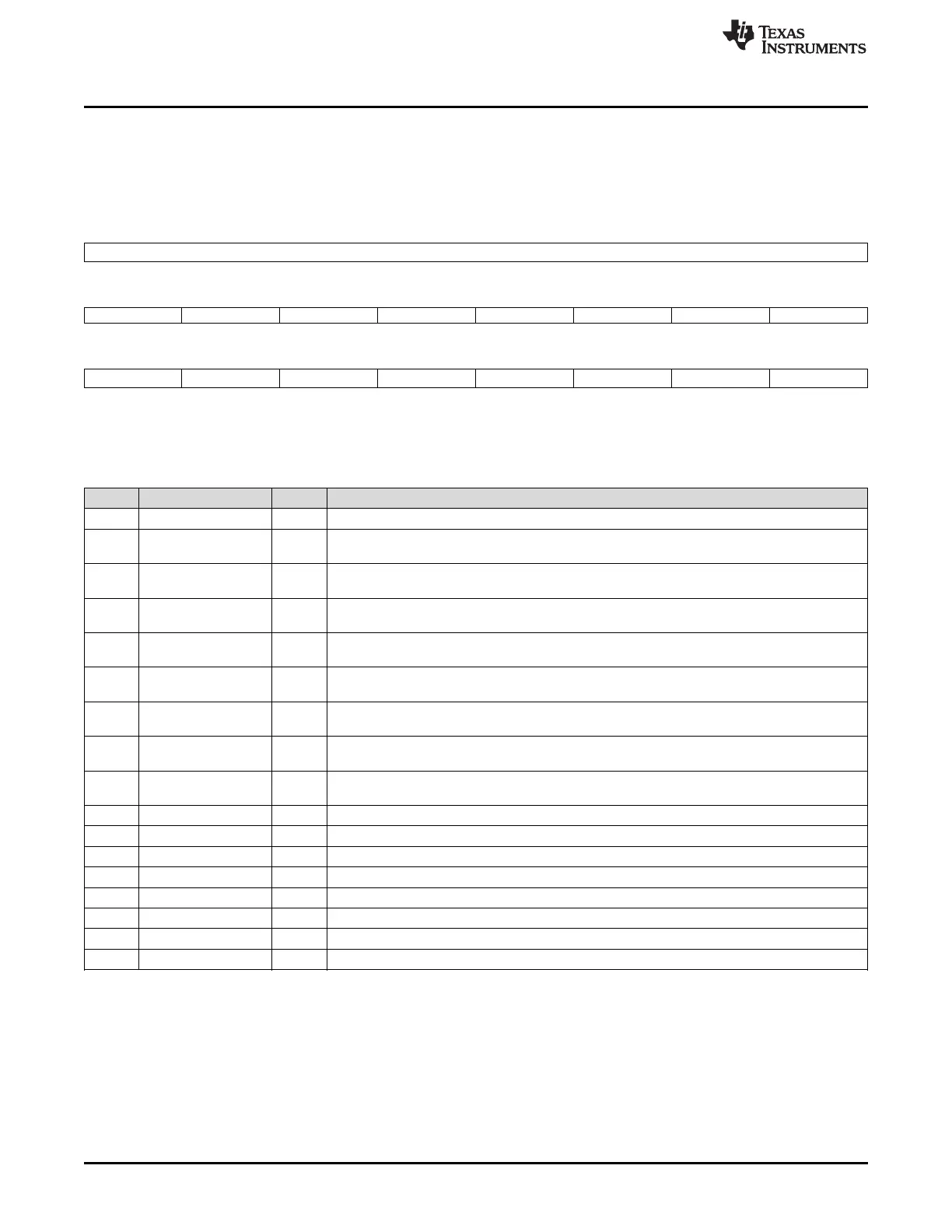

Table 17-53. Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reserved

15 RX7THRESHMASK 0-1 Receive channel 7 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

14 RX6THRESHMASK 0-1 Receive channel 6 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

13 RX5THRESHMASK 0-1 Receive channel 5 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

12 RX4THRESHMASK 0-1 Receive channel 4 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

11 RX3THRESHMASK 0-1 Receive channel 3 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

10 RX2THRESHMASK 0-1 Receive channel 2 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

9 RX1THRESHMASK 0-1 Receive channel 1 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

8 RX0THRESHMASK 0-1 Receive channel 0 threshold mask clear bit. Write 1 to disable interrupt; a write of 0 has no

effect.

7 RX7MASK 0-1 Receive channel 7 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

6 RX6MASK 0-1 Receive channel 6 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

5 RX5MASK 0-1 Receive channel 5 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

4 RX4MASK 0-1 Receive channel 4 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

3 RX3MASK 0-1 Receive channel 3 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

2 RX2MASK 0-1 Receive channel 2 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

1 RX1MASK 0-1 Receive channel 1 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

0 RX0MASK 0-1 Receive channel 0 mask clear bit. Write 1 to disable interrupt; a write of 0 has no effect.

Loading...

Loading...