www.ti.com

MPU Registers

89

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Memory Protection Unit (MPU)

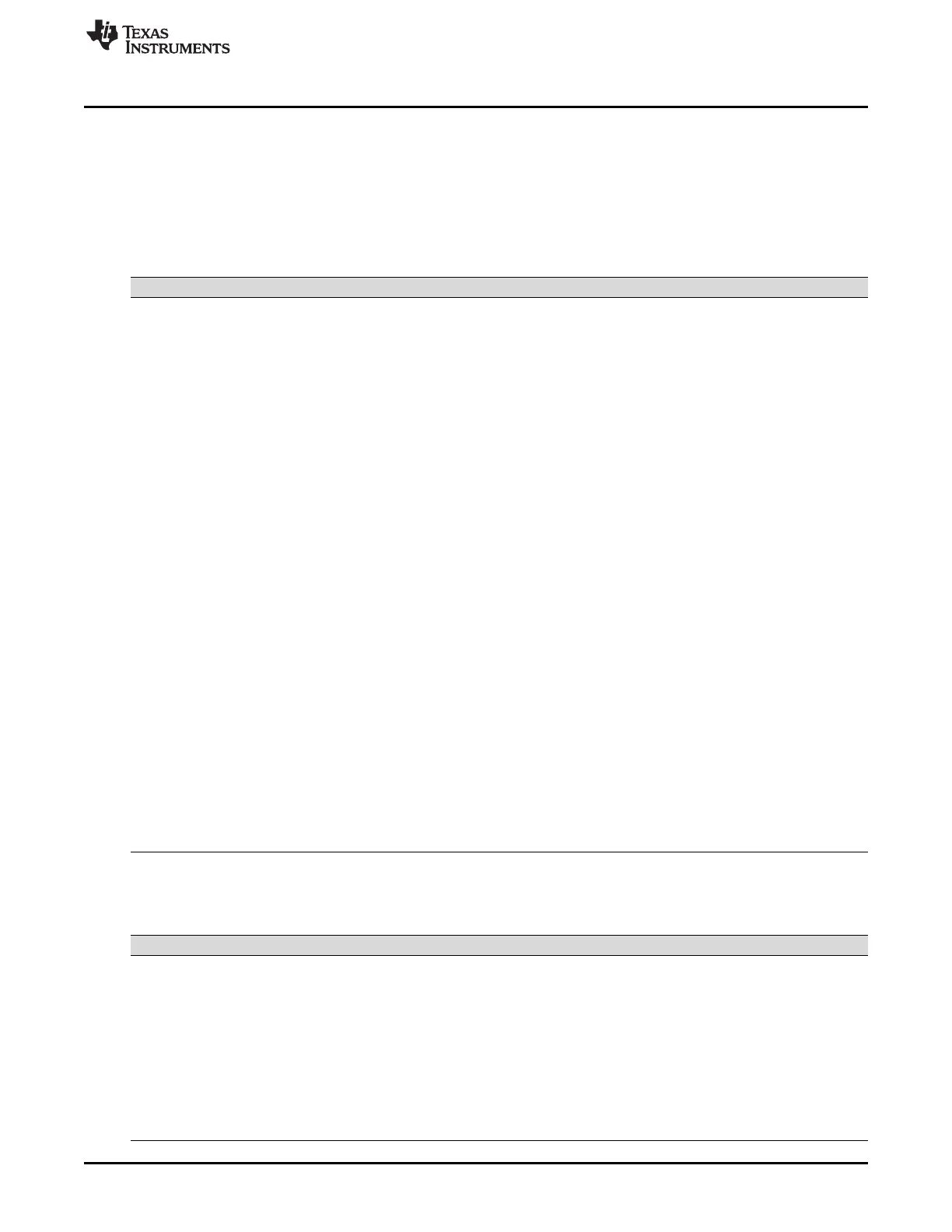

5.3 MPU Registers

There are two MPUs on the device. Each MPU contains a set of memory-mapped registers.

Table 5-6 lists the memory-mapped registers for the MPU1. Table 5-7 lists the memory-mapped registers

for the MPU2.

Table 5-6. Memory Protection Unit 1 (MPU1) Registers

Address Acronym Register Description Section

01E1 4000h REVID Revision identification register Section 5.3.1

01E1 4004h CONFIG Configuration register Section 5.3.2

01E1 4010h IRAWSTAT Interrupt raw status/set register Section 5.3.3

01E1 4014h IENSTAT Interrupt enable status/clear register Section 5.3.4

01E1 4018h IENSET Interrupt enable set register Section 5.3.5

01E1 401Ch IENCLR Interrupt enable clear register Section 5.3.6

01E1 4200h PROG1_MPSAR Programmable range 1 start address register Section 5.3.10.1

01E1 4204h PROG1_MPEAR Programmable range 1 end address register Section 5.3.11.1

01E1 4208h PROG1_MPPA Programmable range 1 memory protection page attributes register Section 5.3.12

01E1 4210h PROG2_MPSAR Programmable range 2 start address register Section 5.3.10.1

01E1 4214h PROG2_MPEAR Programmable range 2 end address register Section 5.3.11.1

01E1 4218h PROG2_MPPA Programmable range 2 memory protection page attributes register Section 5.3.12

01E1 4220h PROG3_MPSAR Programmable range 3 start address register Section 5.3.10.1

01E1 4224h PROG3_MPEAR Programmable range 3 end address register Section 5.3.11.1

01E1 4228h PROG3_MPPA Programmable range 3 memory protection page attributes register Section 5.3.12

01E1 4230h PROG4_MPSAR Programmable range 4 start address register Section 5.3.10.1

01E1 4234h PROG4_MPEAR Programmable range 4 end address register Section 5.3.11.1

01E1 4238h PROG4_MPPA Programmable range 4 memory protection page attributes register Section 5.3.12

01E1 4240h PROG5_MPSAR Programmable range 5 start address register Section 5.3.10.1

01E1 4244h PROG5_MPEAR Programmable range 5 end address register Section 5.3.11.1

01E1 4248h PROG5_MPPA Programmable range 5 memory protection page attributes register Section 5.3.12

01E1 4250h PROG6_MPSAR Programmable range 6 start address register Section 5.3.10.1

01E1 4254h PROG6_MPEAR Programmable range 6 end address register Section 5.3.11.1

01E1 4258h PROG6_MPPA Programmable range 6 memory protection page attributes register Section 5.3.12

01E1 4300h FLTADDRR Fault address register Section 5.3.13

01E1 4304h FLTSTAT Fault status register Section 5.3.14

01E1 4308h FLTCLR Fault clear register Section 5.3.15

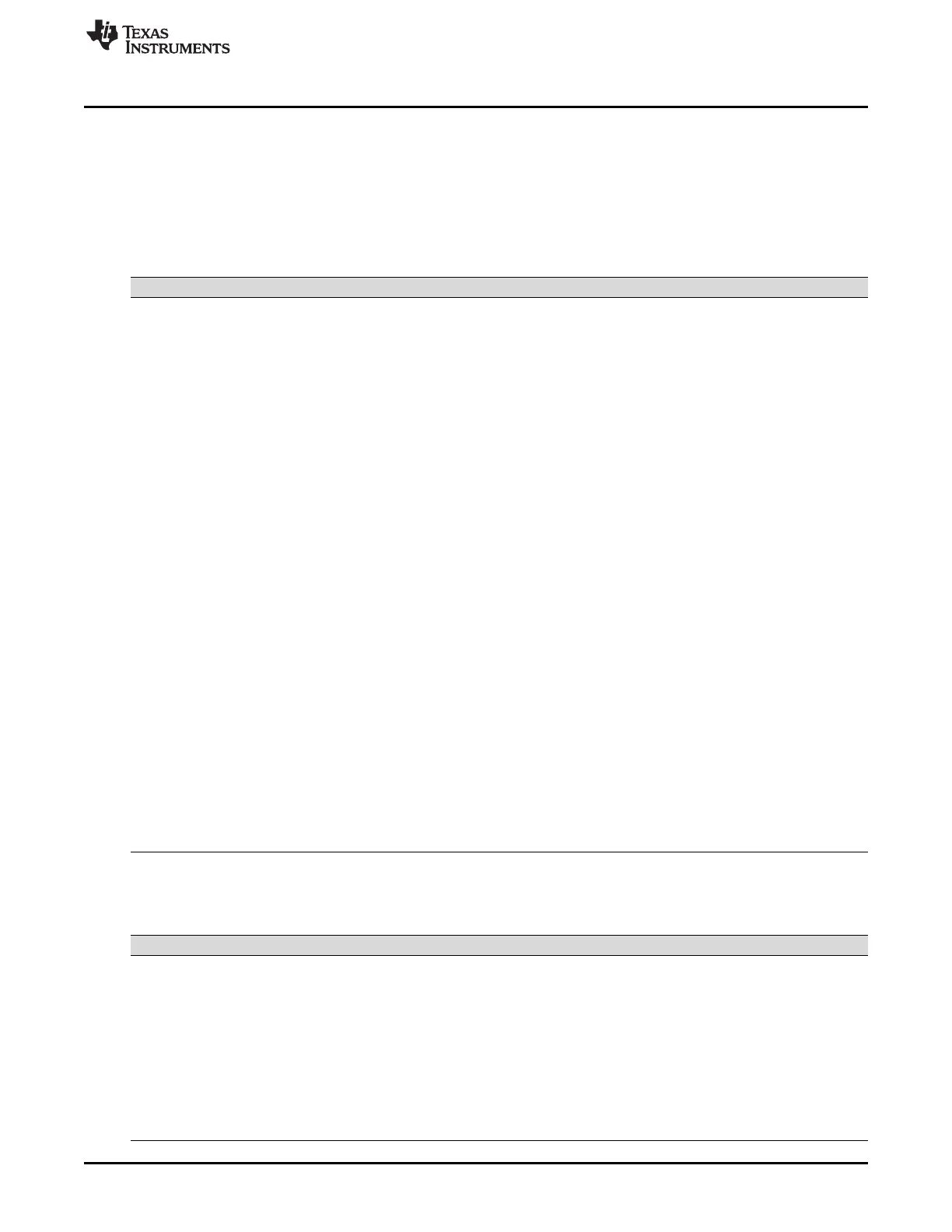

Table 5-7. Memory Protection Unit 2 (MPU2) Registers

Address Acronym Register Description Section

01E1 5000h REVID Revision identification register Section 5.3.1

01E1 5004h CONFIG Configuration register Section 5.3.2

01E1 5010h IRAWSTAT Interrupt raw status/set register Section 5.3.3

01E1 5014h IENSTAT Interrupt enable status/clear register Section 5.3.4

01E1 5018h IENSET Interrupt enable set register Section 5.3.5

01E1 501Ch IENCLR Interrupt enable clear register Section 5.3.6

01E1 5100h FXD_MPSAR Fixed range start address register Section 5.3.7

01E1 5104h FXD_MPEAR Fixed range end address register Section 5.3.8

01E1 5108h FXD_MPPA Fixed range memory protection page attributes register Section 5.3.9

Loading...

Loading...