Bank

Row Col.

D1 D2 D3 D4

EMB_CLK

EMB_CS

EMB_WE_DQM

EMB_BA

EMB_A

EMB_D

EMB_RAS

EMB_WE

EMB_CAS

CL=3

READ

ACTV

www.ti.com

Architecture

795

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface B (EMIFB)

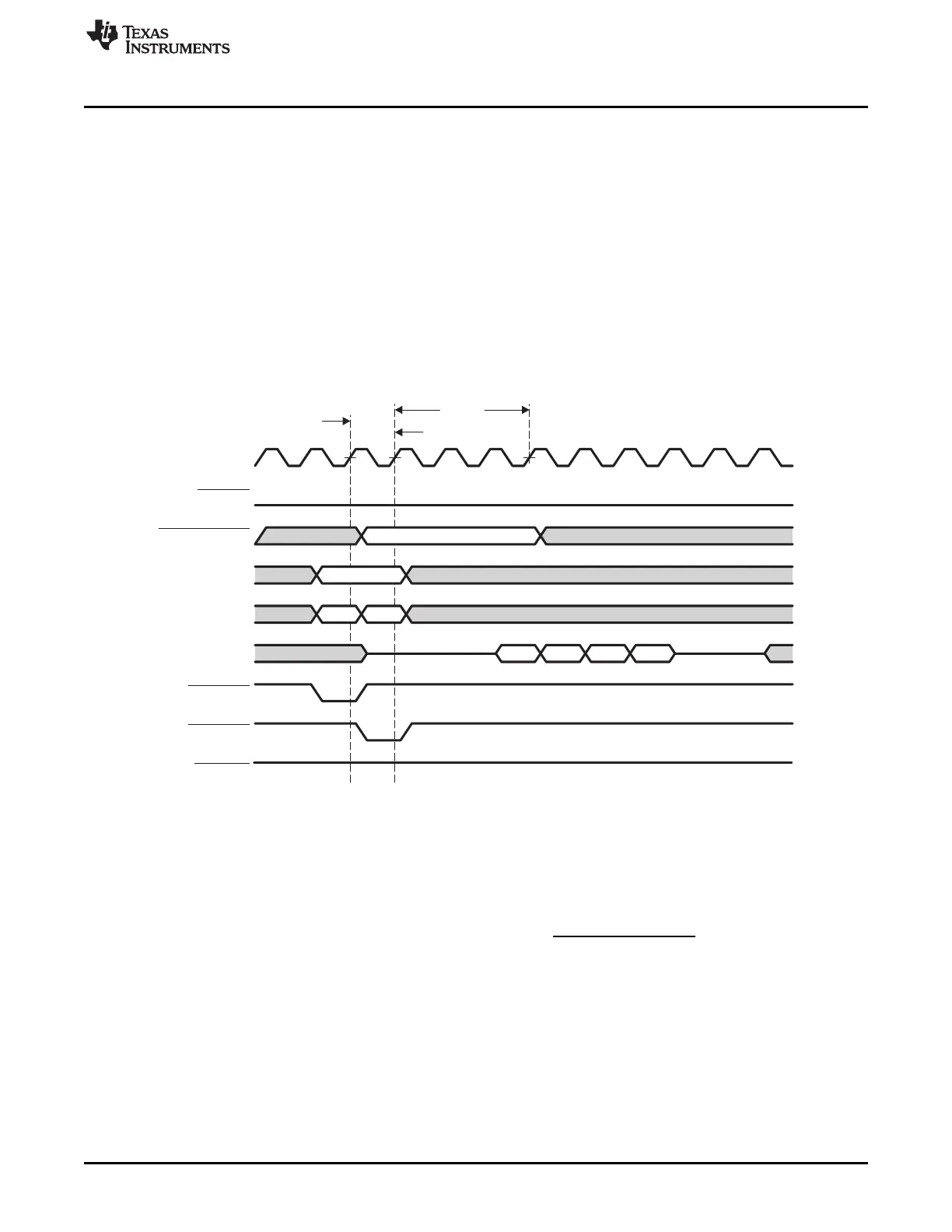

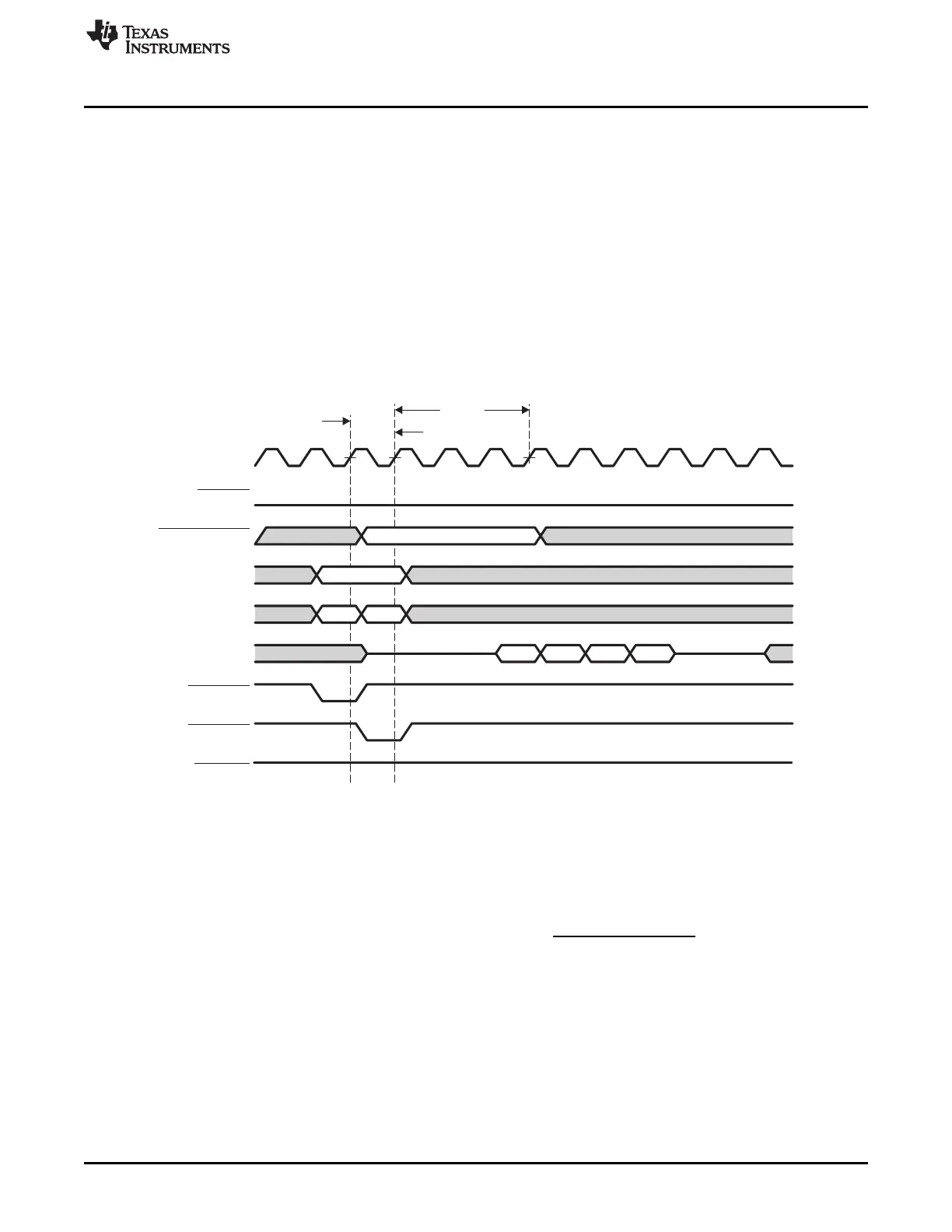

19.2.6.8 SDRAM Read Operation

When the EMIFB receives a read request to SDRAM , it performs one or more read access cycles. A read

access cycle begins with the issuing of the ACTV command to select the desired bank and row of the

SDRAM device. After the row has been opened, the EMIFB proceeds to issue a READ command while

specifying the desired bank and column address. EMB_A[10] is held low during the READ command to

avoid auto-precharging. The READ command signals the SDRAM device to start bursting data from the

specified address while the EMIFB issues NOP commands. Following a READ command, the CL field of

the SDRAM configuration register (SDCFG) defines how many delay cycles will be present before the

read data appears on the data bus. This is referred to as the CAS latency.

Figure 19-6 shows the signal waveforms for a basic SDRAM read operation in which a burst of data is

read from a single page. When the EMIFB SDRAM interface is configured to 32-bit by clearing the NM bit

of the SDRAM configuration register (SDCFG) to 0, a burst size of four is used. When configured to 16-bit

by setting NM to 1, a burst size of eight is used. Figure 19-6 shows a burst size of four.

Figure 19-6. Timing Waveform for Basic SDRAM Read Operation

The EMIFB will truncate a series of bursting data if the remaining addresses of the burst are not required

to complete the request. The EMIFB can truncate the burst in three ways:

• By issuing another READ to the same page in the same bank.

• By issuing a PRE command in order to prepare for accessing a different page of the same bank.

• By issuing a BT command in order to prepare for accessing a page in a different bank.

Several other pins are also active during a read access. The EMB_WE_DQM[3:0] pins are driven low

during the READ commands and are kept low during the NOP commands that correspond to the burst

request. The state of the other EMIFB pins during each command can be found in Table 19-3.

The EMIFB schedules its commands based on the timing information that is provided to it in the SDRAM

timing registers (SDTIM1 and SDTIM2). The values for the timing parameters in this register are chosen to

satisfy the timing requirements listed in the SDRAM datasheet. The EMIFB uses this timing information to

avoid violating any timing constraints related to issuing commands. This is commonly accomplished by

inserting NOP commands between various commands during an access. Refer to the register description

of SDTIM1 and SDTIM2 for more details on the various timing parameters.

Loading...

Loading...