DMA/QDMA

channel

logic

PaRAM

Transfer

request

submission

Completion

anderror

interrupt

logic

EDMA3CC_INT[1:0]

EDMA3CC_ERRINT

Completion

detection

To/from

EDMA3

programmer

Channelcontroller

TC0

Transfer

controllers

Read/write

commands

anddata

EDMA3TC_

ERRINT0

MMR

TC1

commands

Read/write

anddata

MMR

EDMA3TC_

ERRINT1

Event

queue

EDMA3CC_GINT

www.ti.com

Introduction

439

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

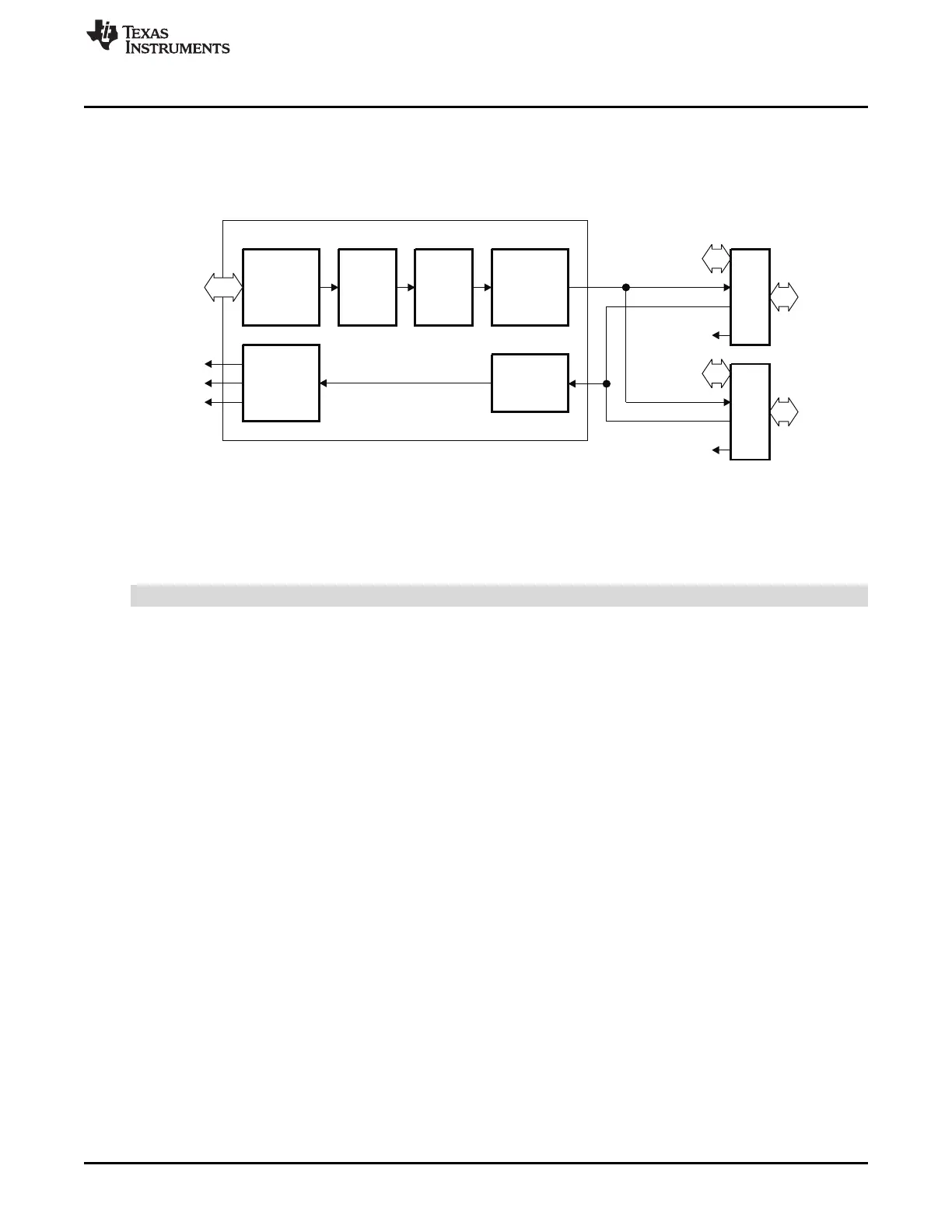

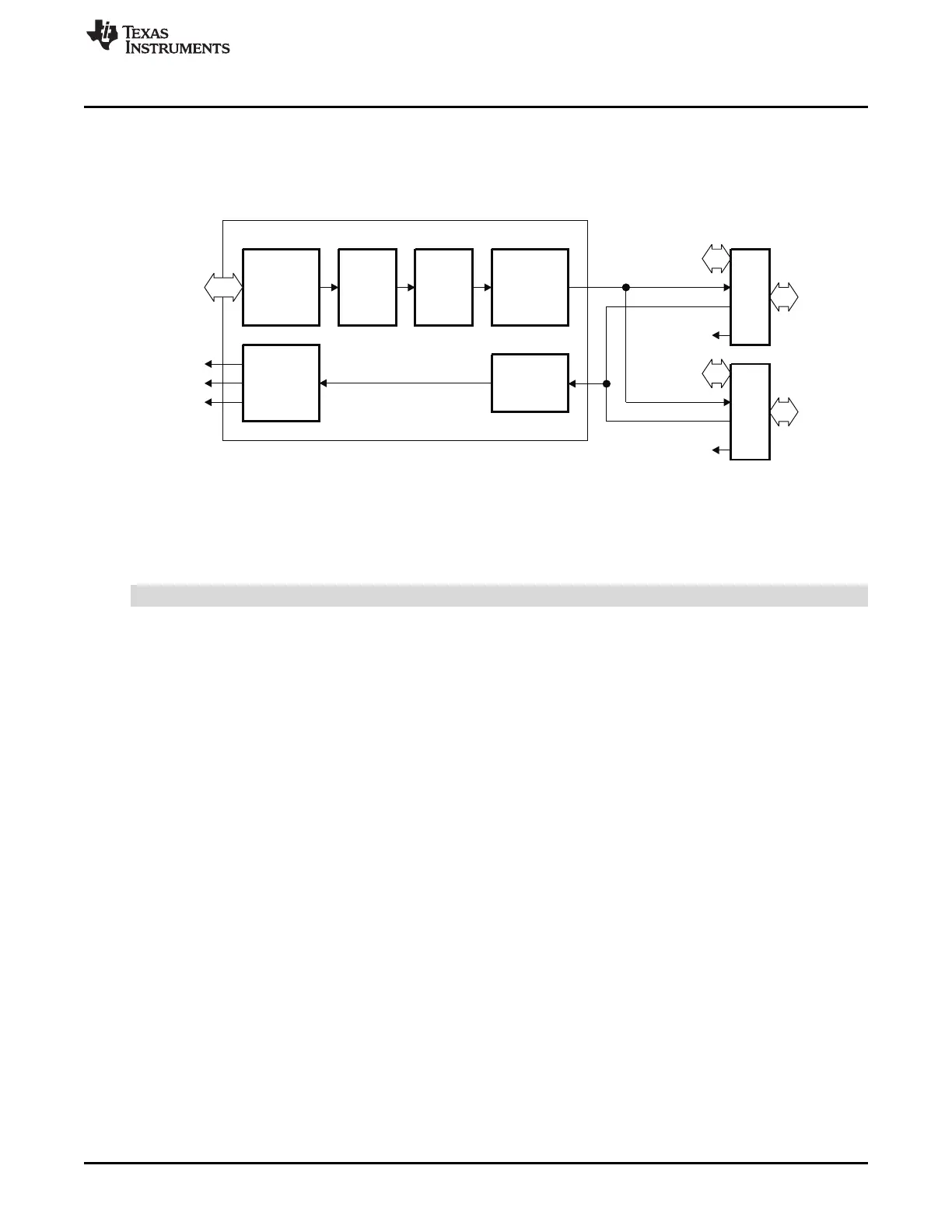

16.1.3 Functional Block Diagram

Figure 16-1 shows a block diagram of the EDMA3 controller.

Figure 16-1. EDMA3 Controller Block Diagram

16.1.4 Terminology Used in This Document

The following are some terms used in this chapter.

Term Meaning

A-synchronized

transfer

A transfer type where 1 dimension is serviced per synchronization event.

AB-synchronized

transfer

A transfer type where 2 dimensions are serviced per synchronization event.

Chaining A trigger mechanism in which a transfer can be initiated at the completion of

another transfer or subtransfer.

CPU(s) The main processing engine or engines on a device. Typically a DSP or general-

purpose processor. (See your device-specific data manual to learn more about the

CPU on your system.)

DMA channel A channel that can be triggered by external, manual, and chained events. All DMA

channels exist in the EDMA3CC.

Dummy set or

Dummy PaRAM set

A PaRAM set for which at least one of the count fields is equal to 0 and at least

one of the count fields is nonzero. A null PaRAM set has all the count set fields

cleared.

Dummy transfer A dummy set results in the EDMA3CC performing a dummy transfer. This is not an

error condition. A null set results in an error condition.

EDMA3 channel

controller

(EDMA3CC)

The user-programmable portion of the EDMA3. The EDMA3CC contains the

parameter RAM (PaRAM) , event processing logic, DMA/QDMA channels, event

queues, etc. The EDMA3CC services events (external, manual, chained, QDMA)

and is responsible for submitting transfer requests to the transfer controllers

(EDMA3TC), which perform the actual transfer.

EDMA3

programmer

Any entity on the chip that has read/write access to the EDMA3 registers and can

program an EDMA3 transfer.

EDMA3 transfer

controller(s)

(EDMA3TC)

Transfer controllers are the transfer engine for the EDMA3. Performs the

read/writes as dictated by the transfer requests submitted by the EDMA3CC.

Loading...

Loading...