Architecture

www.ti.com

460

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

16.2.5 Completion of a DMA Transfer

A parameter set for a given channel is complete when the required number of transfer requests is

submitted (based on receiving the number of synchronization events). The expected number of TRs for a

non-null/non-dummy transfer is shown in Table 16-4 for both synchronization types along with state of the

PaRAM set prior to the final TR being submitted. When the counts (BCNT and/or CCNT) are this value,

the next TR results in a:

• Final chaining or interrupt codes to be sent by the transfer controllers (instead of intermediate).

• Link updates (linking to either null or another valid link set).

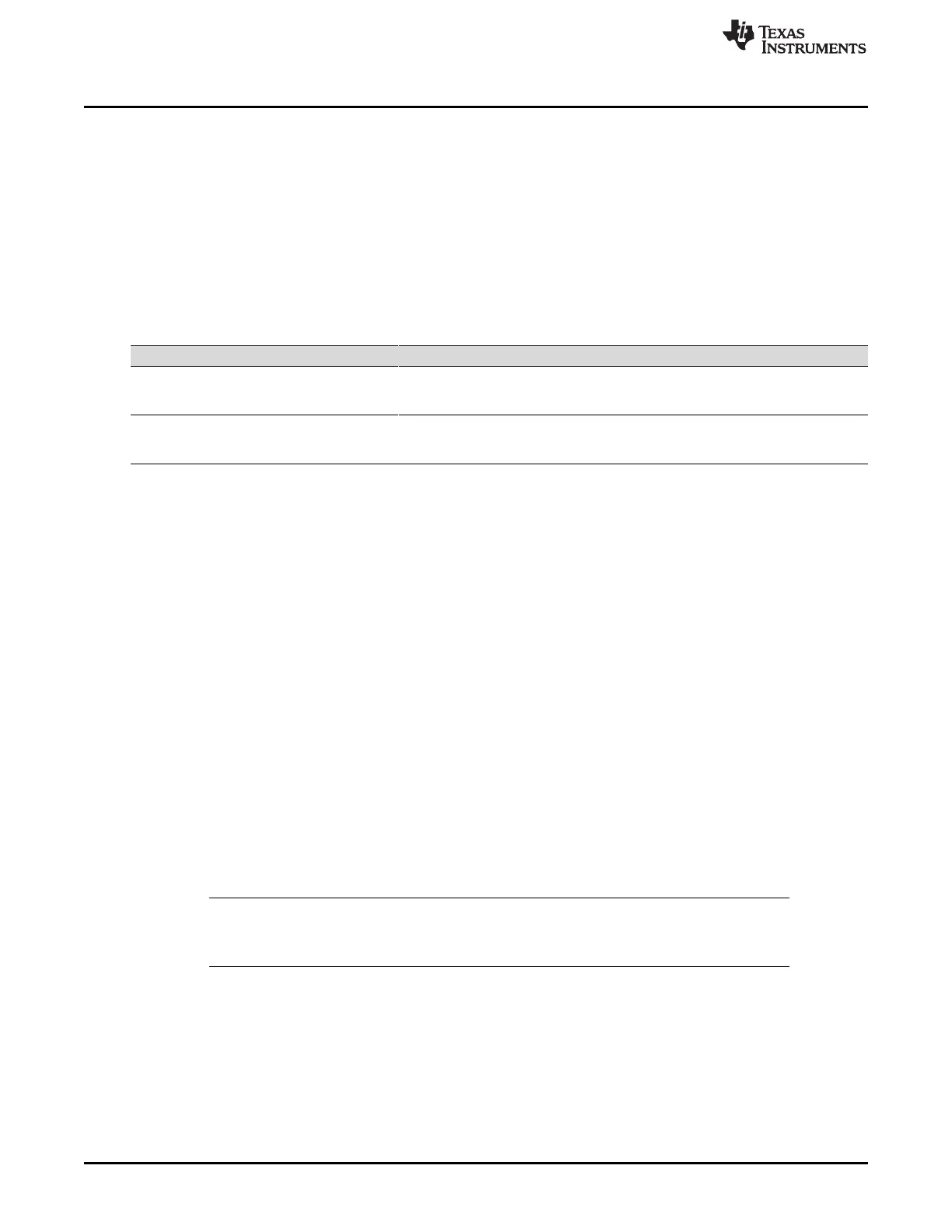

Table 16-4. Expected Number of Transfers for Non-Null Transfer

Sync Mode Counts at time 0 Total # Transfers Counts prior to final TR

A-synchronized ACNT

BCNT

CCNT

(BCNT × CCNT ) TRs of ACNT bytes each BCNT == 1 && CCNT == 1

AB-synchronized ACNT

BCNT

CCNT

CCNT TRs for ACNT × BCNT bytes each CCNT == 1

You must program the PaRAM OPT field with a specific transfer completion code (TCC) along with the

other OPT fields (TCCHEN, TCINTEN, ITCCHEN, and ITCINTEN bits) to indicate whether the completion

code is to be used for generating a chained event or/and for generating an interrupt upon completion of a

transfer.

The specific TCC value (6-bit binary value) programmed dictates which of the 64-bits in the chain event

register (CER[TCC]) and/or interrupt pending register (IPR[TCC]) is set.

See Section 16.2.9 for details on interrupts and Section 16.2.8 for details on chaining.

You can also selectively program whether the transfer controller sends back completion codes on

completion of the final transfer request (TR) of a parameter set (TCCHEN or TCINTEN), for all but the

final transfer request (TR) of a parameter set (ITCCHEN or ITCINTEN), or for all TRs of a parameter set

(both). See Section 16.2.8 for details on chaining (intermediate/final chaining) and Section 16.2.9 for

details on intermediate/final interrupt completion.

A completion detection interface exists between the EDMA3 channel controller and transfer controller(s).

This interface sends back information from the transfer controller to the channel controller to indicate that

a specific transfer is completed.

All DMA/QDMA PaRAM sets must also specify a link address value. For repetitive transfers such as ping-

pong buffers, the link address value should point to another predefined PaRAM set. Alternatively, a

nonrepetitive transfer should set the link address value to the null link value. The null link value is defined

as FFFFh. See Section 16.2.3.7 for more details.

NOTE: Any incoming events that are mapped to a null PaRAM set results in an error condition. The

error condition should be cleared before the corresponding channel is used again. See

Section 16.2.3.5.

There are three ways the EDMA3CC gets updated/informed about a transfer completion: normal

completion, early completion, and dummy/null completion. This applies to both chained events and

completion interrupt generation.

Loading...

Loading...