www.ti.com

Registers

273

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Capture (eCAP) Module

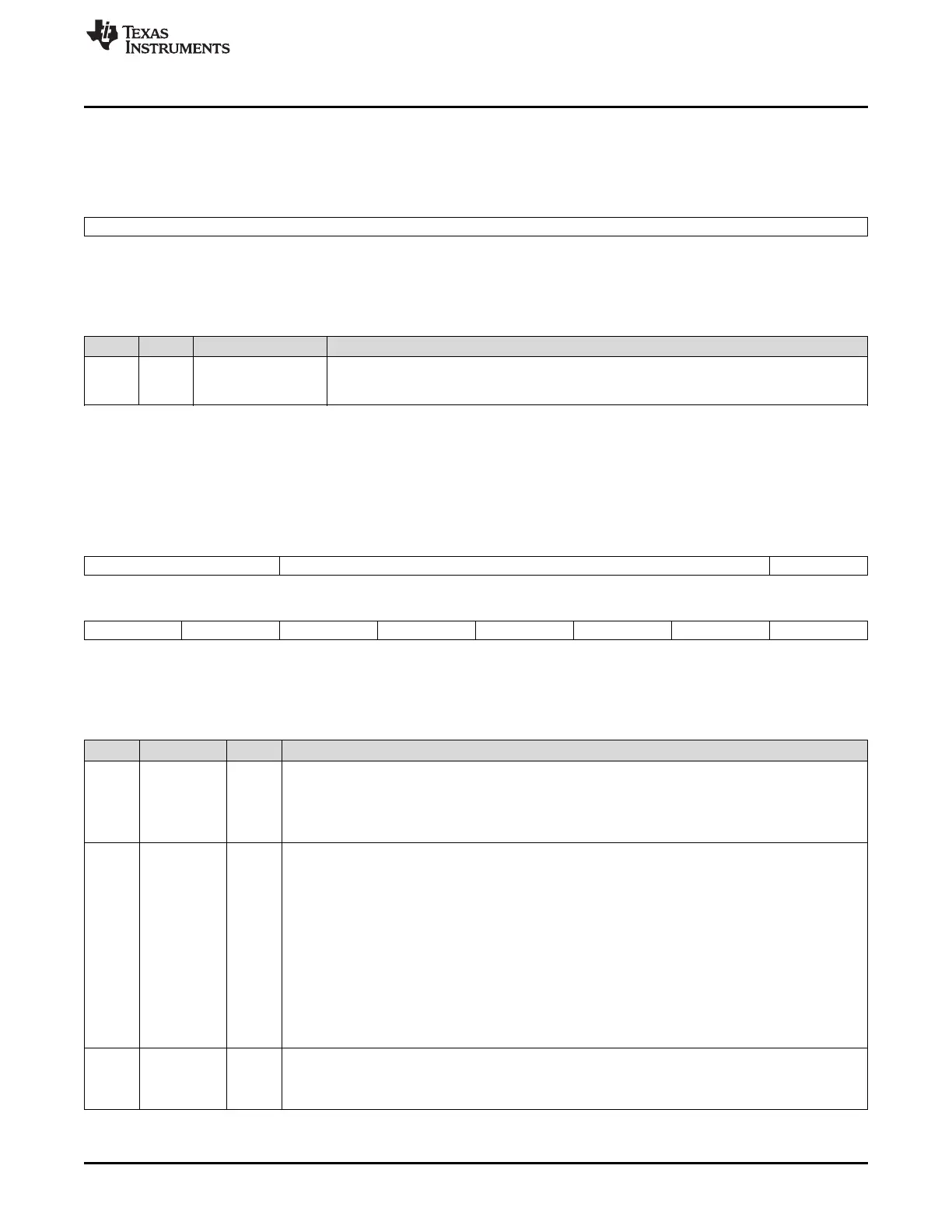

13.4.6 Capture 4 Register (CAP4)

The capture 4 register (CAP4) is shown in Figure 13-22 and described in Table 13-19.

Figure 13-22. Capture 4 Register (CAP4)

31 0

CAP4

R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

Table 13-19. Capture 4 Register (CAP4) Field Descriptions

Bit Field Value Description

31-0 CAP4 0-FFFF FFFFh In CMP mode, this is a time-stamp capture register. In APWM mode, this is the compare

shadow (ACMP) register. You update the PWM compare value through this register. In this

mode, CAP4 shadows CAP2.

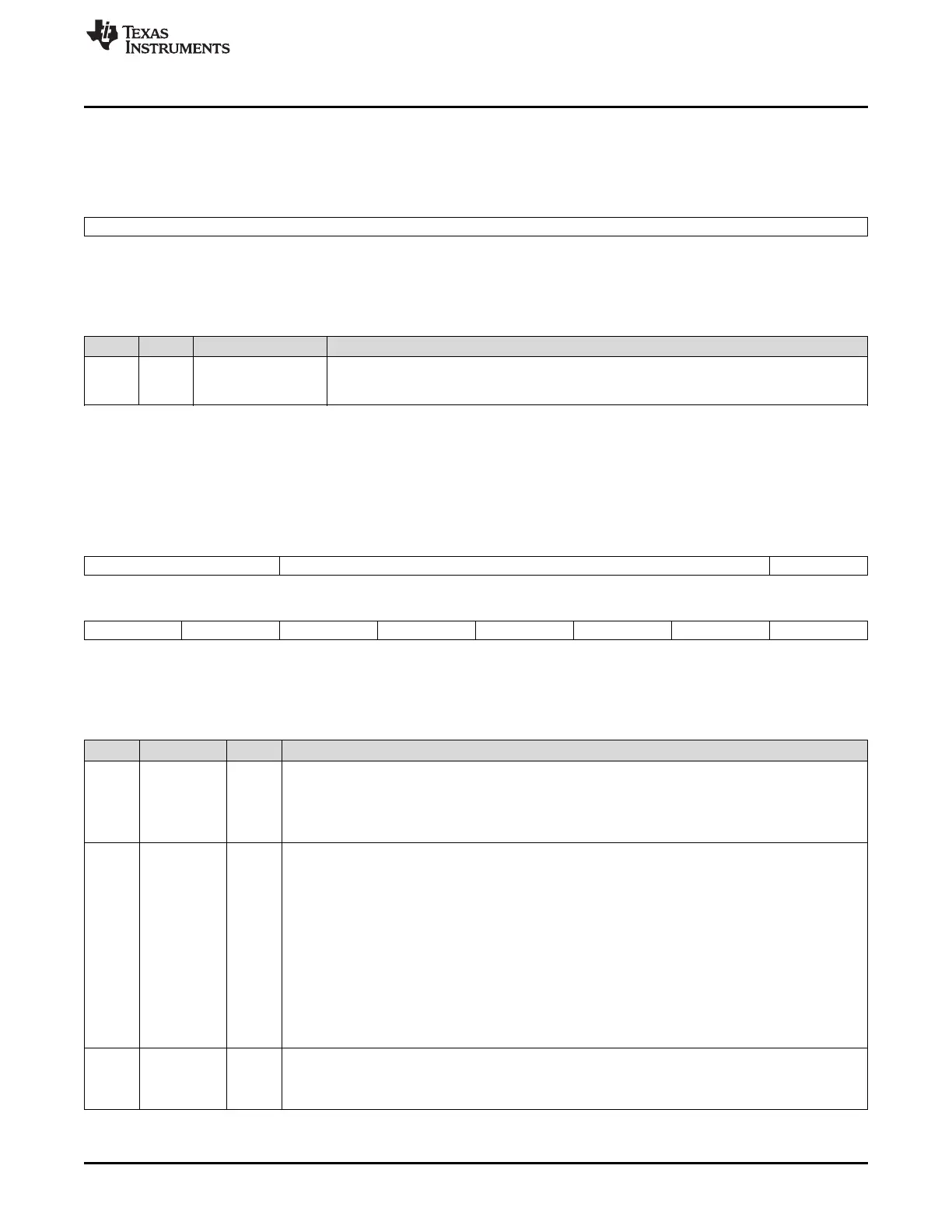

13.4.7 ECAP Control Register 1 (ECCTL1)

The ECAP control register 1 (ECCTL1) is shown in Figure 13-23 and described in Table 13-20.

Figure 13-23. ECAP Control Register 1 (ECCTL1)

15 14 13 9 8

FREE/SOFT PRESCALE CAPLDEN

R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

CTRRST4 CAP4POL CTRRST3 CAP3POL CTRRST2 CAP2POL CTRRST1 CAP1POL

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

Table 13-20. ECAP Control Register 1 (ECCTL1) Field Descriptions

Bit Field Value Description

15-14 FREE/SOFT 0-3h Emulation Control

0 TSCTR counter stops immediately on emulation suspend

1h TSCTR counter runs until = 0

2h-3h TSCTR counter is unaffected by emulation suspend (Run Free)

13-9 PRESCALE 0-1Fh Event Filter prescale select

0 Divide by 1 (i.e,. no prescale, by-pass the prescaler)

1 Divide by 2

2h Divide by 4

3h Divide by 6

4h Divide by 8

5h Divide by 10

...

1Eh Divide by 60

1Fh Divide by 62

8 CAPLDEN Enable Loading of CAP1-4 registers on a capture event

0 Disable CAP1-4 register loads at capture event time.

1 Enable CAP1-4 register loads at capture event time.

Loading...

Loading...