Architecture

www.ti.com

346

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced High-Resolution Pulse-Width Modulator (eHRPWM)

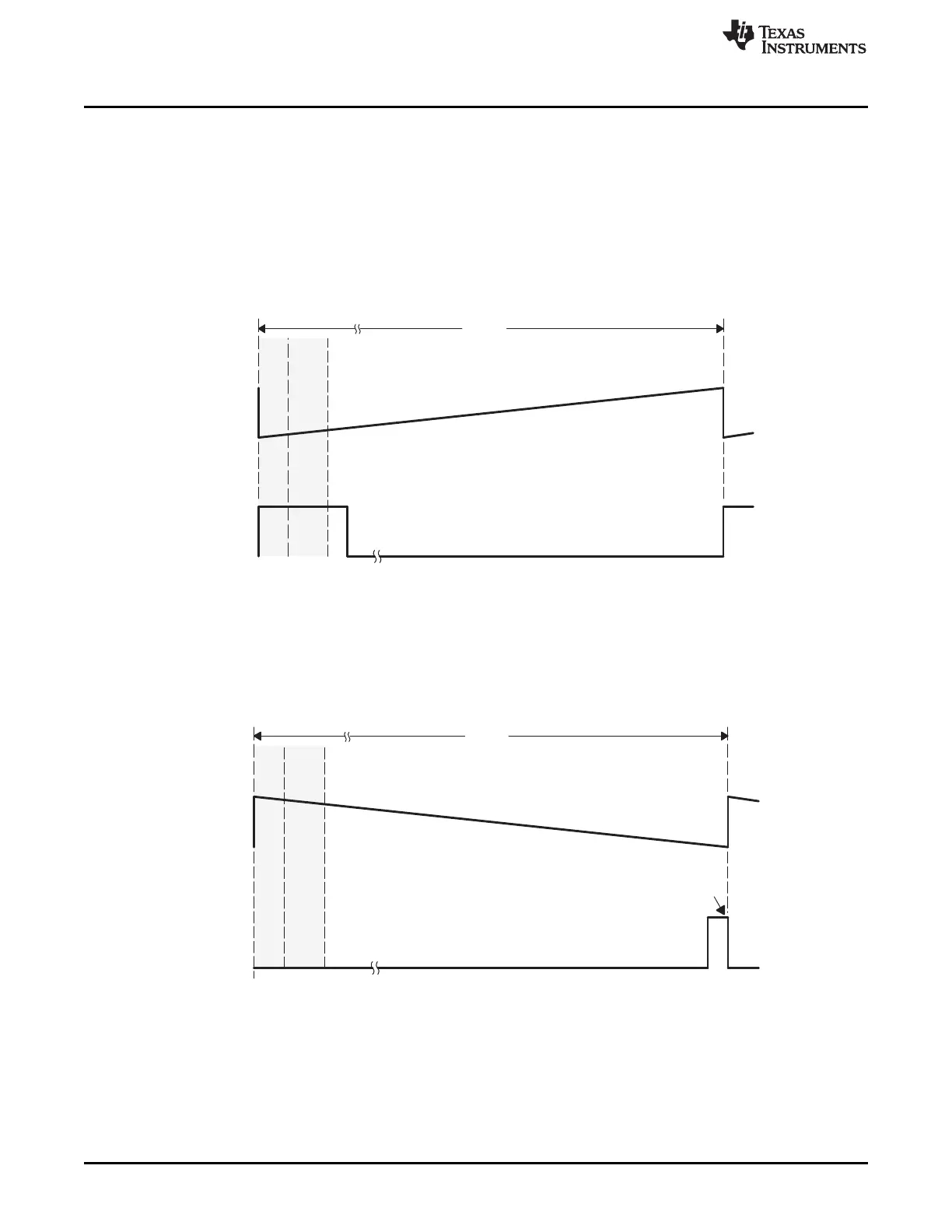

14.2.10.5.3 Duty Cycle Range Limitation

In high resolution mode, the MEP is not active for 100% of the PWM period. It becomes operational

3 SYSCLK cycles after the period starts.

Duty cycle range limitations are illustrated in Figure 14-47. This limitation imposes a lower duty cycle limit

on the MEP. For example, precision edge control is not available all the way down to 0% duty cycle.

Although for the first 3 or 6 cycles, the HRPWM capabilities are not available, regular PWM duty control is

still fully operational down to 0% duty. In most applications this should not be an issue as the controller

regulation point is usually not designed to be close to 0% duty cycle.

Figure 14-47. Low % Duty Cycle Range Limitation Example When PWM Frequency = 1 MHz

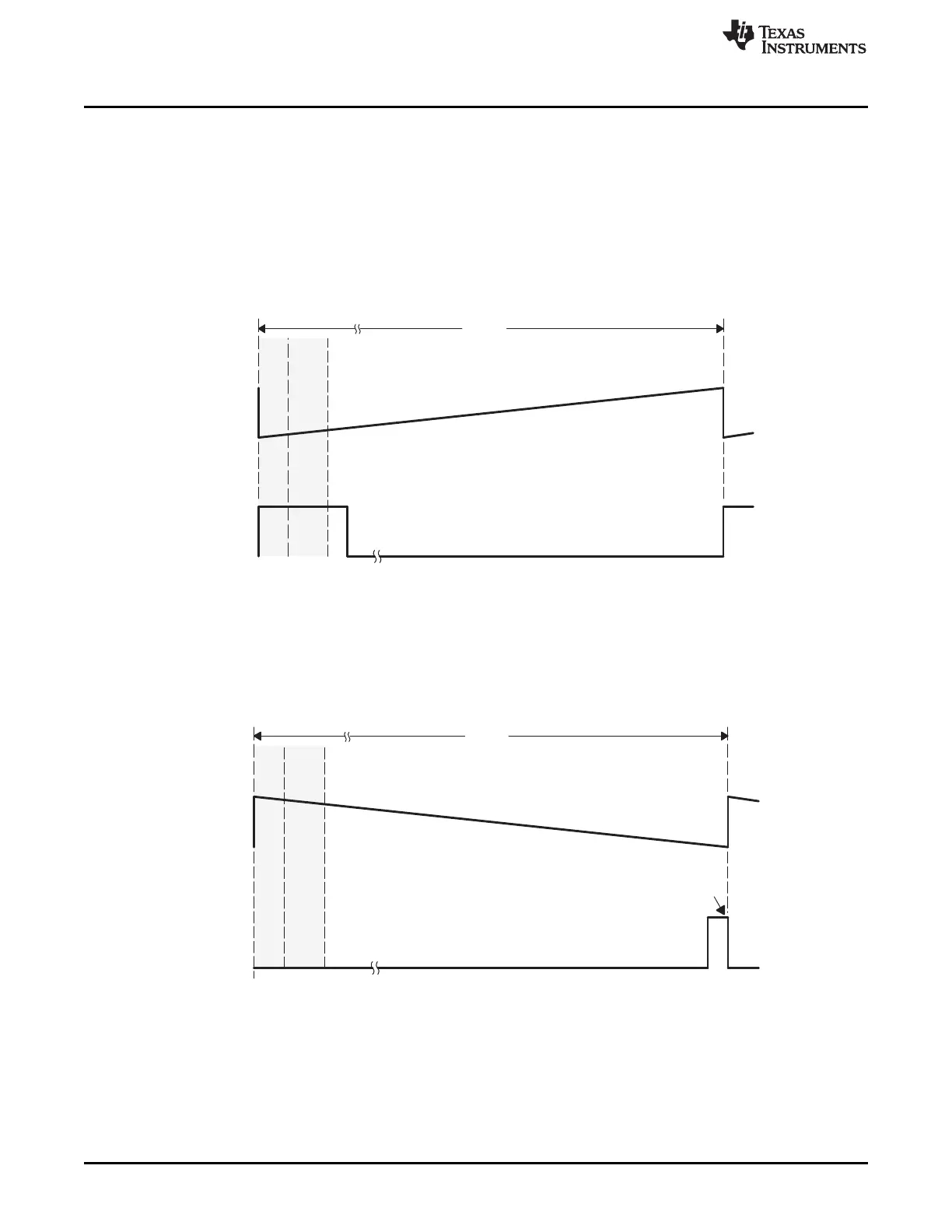

If the application demands HRPWM operation in the low percent duty cycle region, then the HRPWM can

be configured to operate in count-down mode with the rising edge position (REP) controlled by the MEP.

This is illustrated in Figure 14-48. In this case low percent duty limitation is no longer an issue.

Figure 14-48. High % Duty Cycle Range Limitation Example when PWM Frequency = 1 MHz

Loading...

Loading...