1

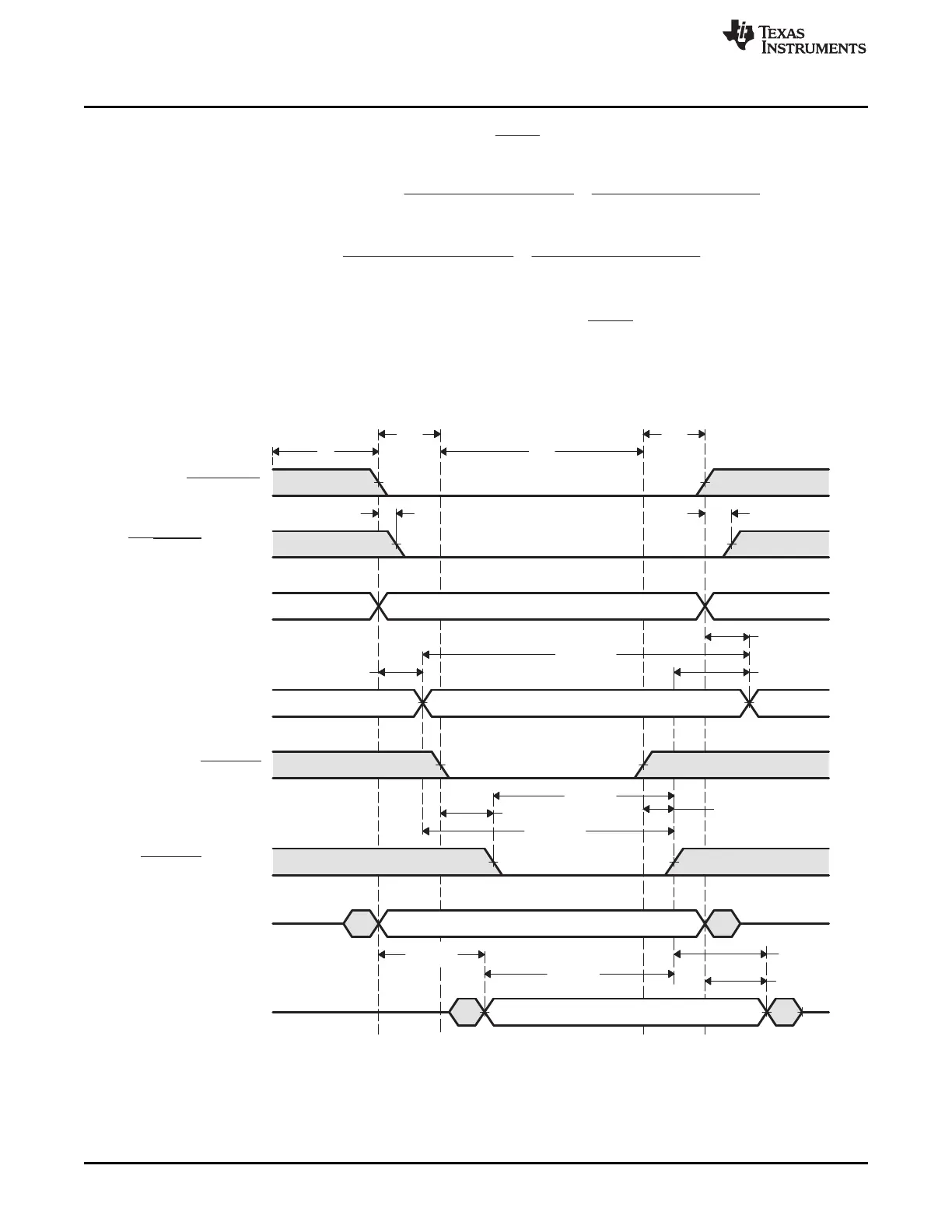

Setup

2

Strobe

3

Hold

4

EMA_CS[n]

EMA_CS[n] (ASRAM)

EMA_A[x:0]/

EMA_BA[1:0]

EMA_A[x:0]/

EMA_BA[1:0] (ASRAM)

EMA_WE

EMA_WE (ASRAM)

EMA_D[x:0]

EMA_D[x:0] (ASRAM)

t

EMA_CS

t

EMA_CS

t

EMA_A

t

WC

(m)

t

WR

(m)

t

EMA_A

t

WP

(m)

t

EMA_WE

t

AW

(m)

t

EMA_WE

t

EMA_D

t

DS

(m)

t

EMA_D

t

DH

(m)

W_SETUP ) W_STROBE ) W_HOLD w

t

WC

(m)

t

cyc

* 3

W_HOLD w max

ǒ

ǒ

t

EM_WE

) t

WR

(m) * t

EM_A

Ǔ

t

cyc

,

ǒ

t

EM_WE

) t

DH

(m) * t

EM_D

Ǔ

t

cyc

Ǔ

* 1

W_SETUP + W_STROBE ≥

max

t

EM_A

t

AW

(m) t

EM_WE

t

cyc

,

t

EM_D

t

DS

(m) t

EM_WE

t

cyc

- 2

( )

( ) ( )

+

-

+

-

Example Configuration

www.ti.com

746

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface A (EMIFA)

Figure 18-26. Timing Waveform of an ASRAM Write with PCB Delays

Loading...

Loading...