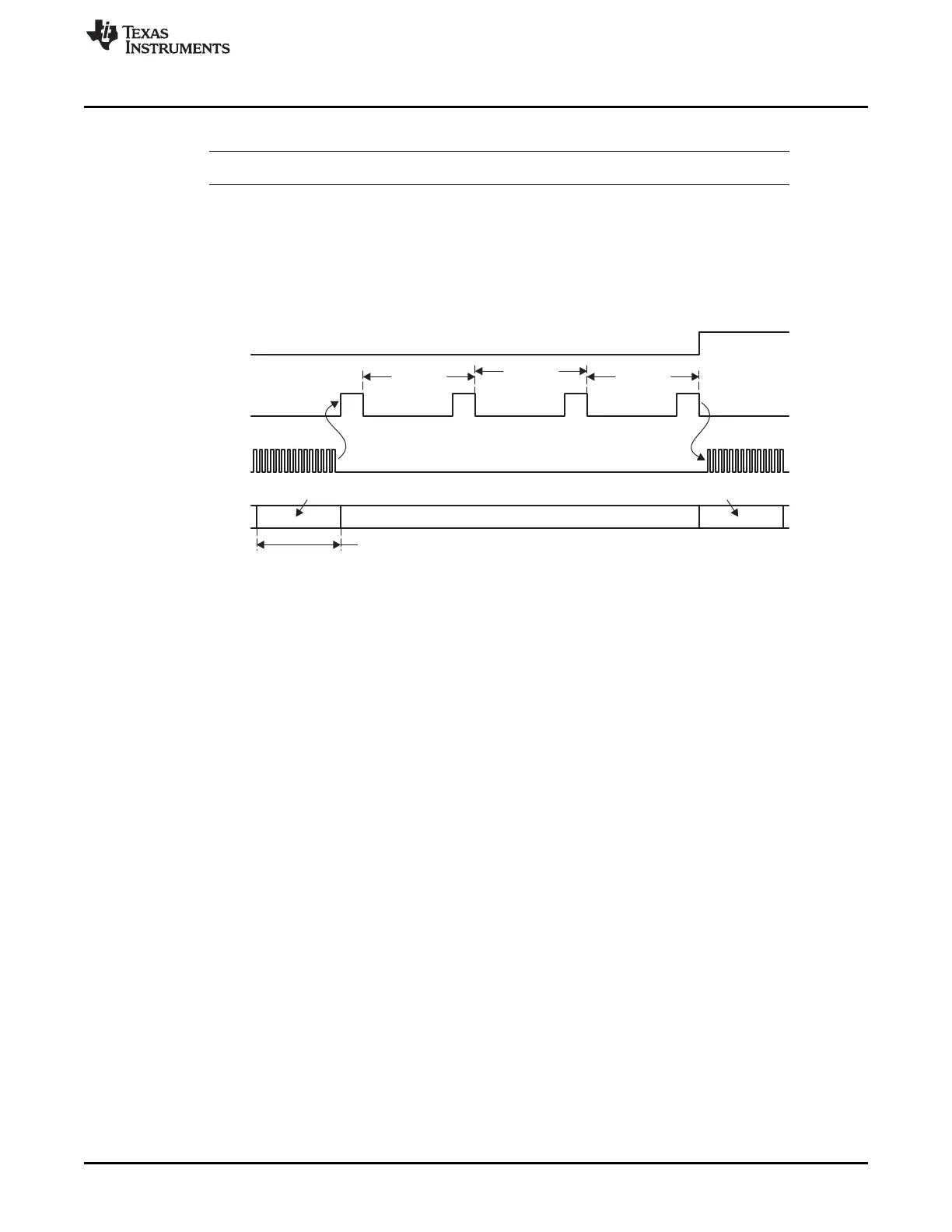

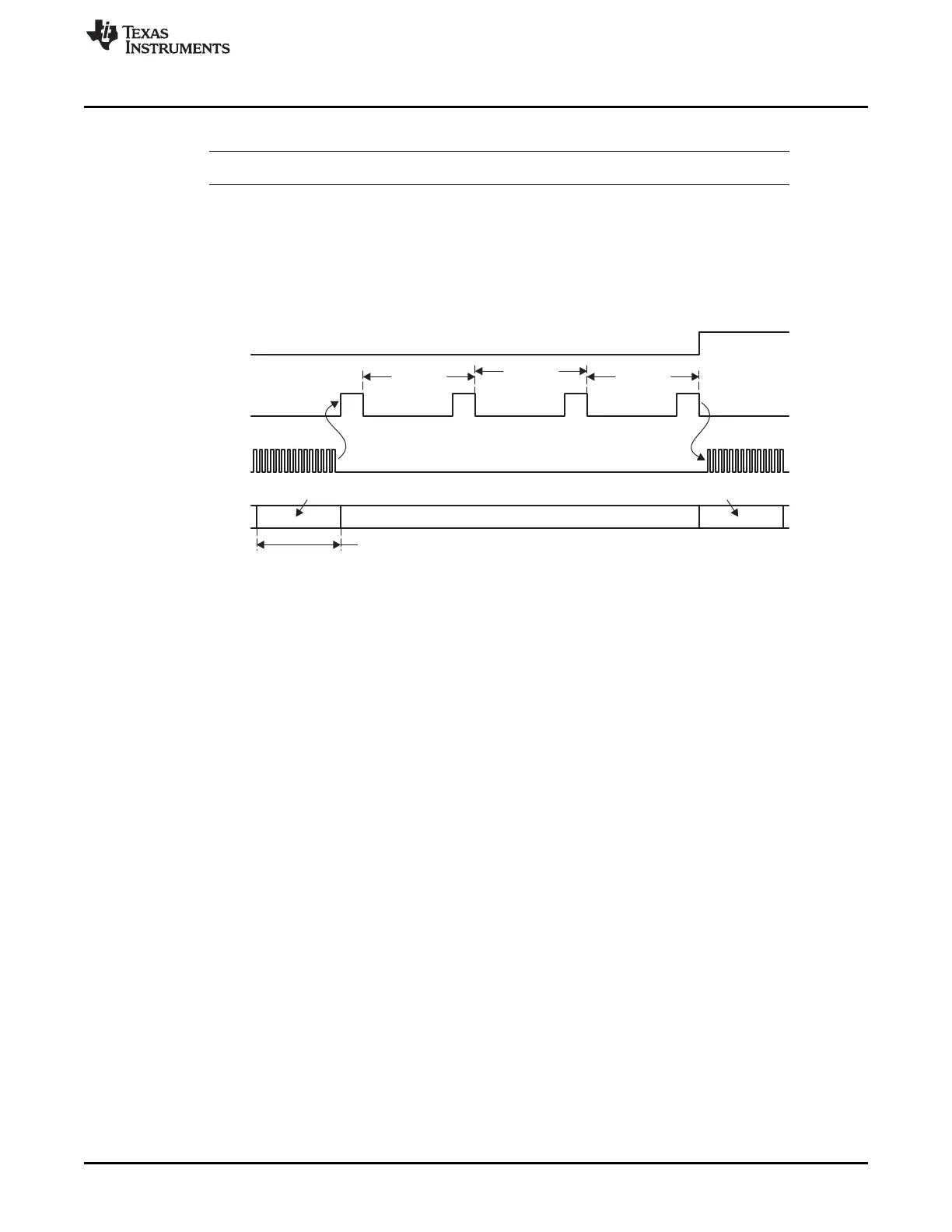

LinePulse

(LCD_HSYNC)

HFP =2

VFP =1

VSW=0

VBP =1

HBP =2

Line479Data

LPP =480

Line0Data

PixelClock

(LCD_PCLK)

Data

(LCD_D[x:0])

FramePulse

(LCD_VSYNC)

www.ti.com

Registers

971

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Liquid Crystal Display Controller (LCDC)

23.3.10.3 Vertical Front Porch (VFP)

NOTE: Remember that VSW must be programmed to value required minus 1.

The 8-bit vertical front porch (VFP) field is used to specify the number of line clocks to insert at the end of

each frame. Once a complete frame of pixels is transmitted to the LCD display, the value in VFP is used

to count the number of line clock periods to wait. After the count has elapsed the LCD_VSYNC signal is

pulsed in active mode or extra line clocks are inserted as specified by the VSW bit-field in passive mode.

VFP generates from 0–255 line clock cycles (see Figure 23-33).

Figure 23-33. Vertical Front Porch (VFP)

Loading...

Loading...