Registers

www.ti.com

552

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

16.4.3.4.3 Error Clear Register (ERRCLR)

The error clear register (ERRCLR) is shown in Figure 16-87 and described in Table 16-67.

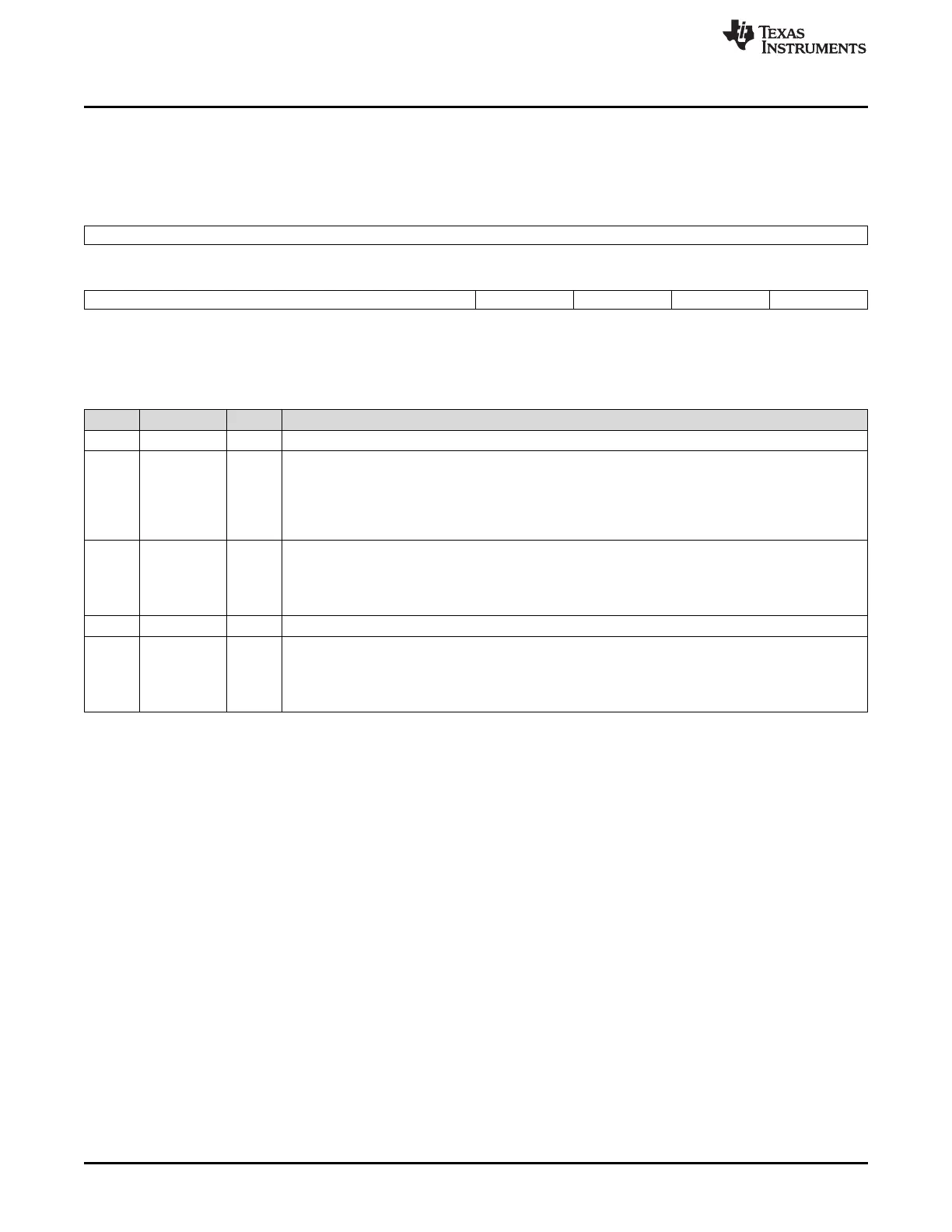

Figure 16-87. Error Clear Register (ERRCLR)

31 16

Reserved

R-0

15 4 3 2 1 0

Reserved MMRAERR TRERR Reserved BUSERR

R-0 W-0 W-0 R-0 W-0

LEGEND: R = Read only; W = Write only; -n = value after reset

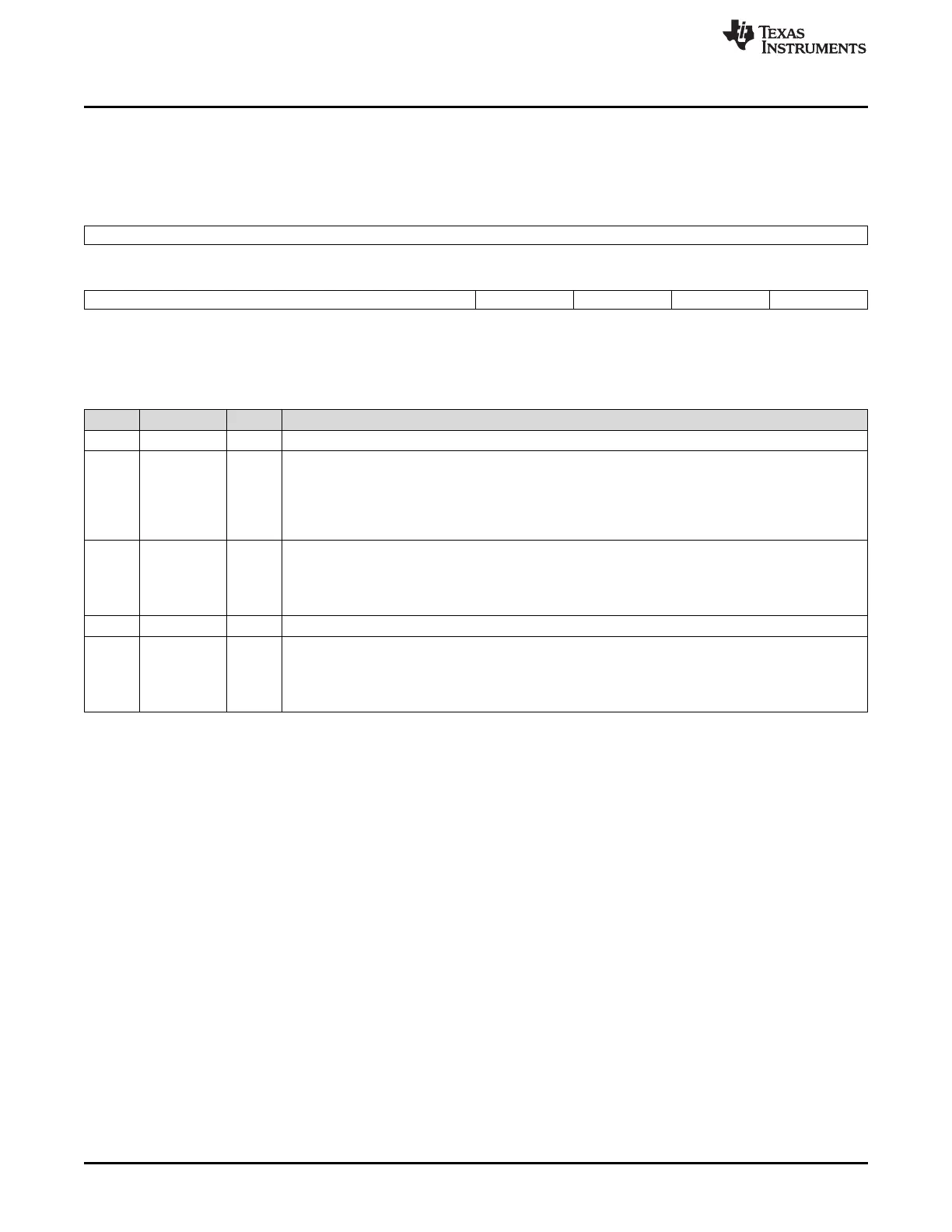

Table 16-67. Error Clear Register (ERRCLR) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reserved

3 MMRAERR Interrupt enable clear for the MMR address error (MMRAERR) bit in the error status register

(ERRSTAT).

0 No effect.

1 Clears the MMRAERR bit in the error status register (ERRSTAT) but does not clear the error details

register (ERRDET).

2 TRERR Interrupt enable clear for the transfer request error (TRERR) bit in the error status register (ERRSTAT).

0 No effect.

1 Clears the TRERR bit in the error status register (ERRSTAT) but does not clear the error details register

(ERRDET).

1 Reserved 0 Reserved

0 BUSERR Interrupt clear for the bus error (BUSERR) bit in the error status register (ERRSTAT).

0 No effect.

1 Clears the BUSERR bit in the error status register (ERRSTAT) and clears the error details register

(ERRDET).

Loading...

Loading...