UHPI_HCS

UHP_HAS

Internal

UHPI_HRDY

UHPI_HD[15:0]

UHPI_HR/W

UHPI_HCNTL[1:0]

HHWIL

10 10 01 01 01

1st halfword2nd halfword1st halfword2nd halfword1st halfword

UHPI_HSTRB

UHPI_HCS

UHPI_HAS

UHPI_HCNTL[1:0]

UHPI_HR/W

UHPI_HHWIL

Internal

HSTRB

UHPI_HD[15:0]

UHPI_HRDY

1st halfword 2nd halfword 1st halfword

2nd halfword

11 111010

1st halfword

00 or 10 00 or 10

2nd halfword

Internal

UHPI_HD[15:0]

UHPI_HRDY

UHPI_HHWIL

UHPI_HR/W

UHPI_HCNTL[1:0]

UHPI_HAS

UHPI_HCS

HSTRB

www.ti.com

Architecture

871

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Host Port Interface (HPI)

21.2.6.9.1 UHPI_HRDY Behavior During Multiplexed-Mode Read Operations

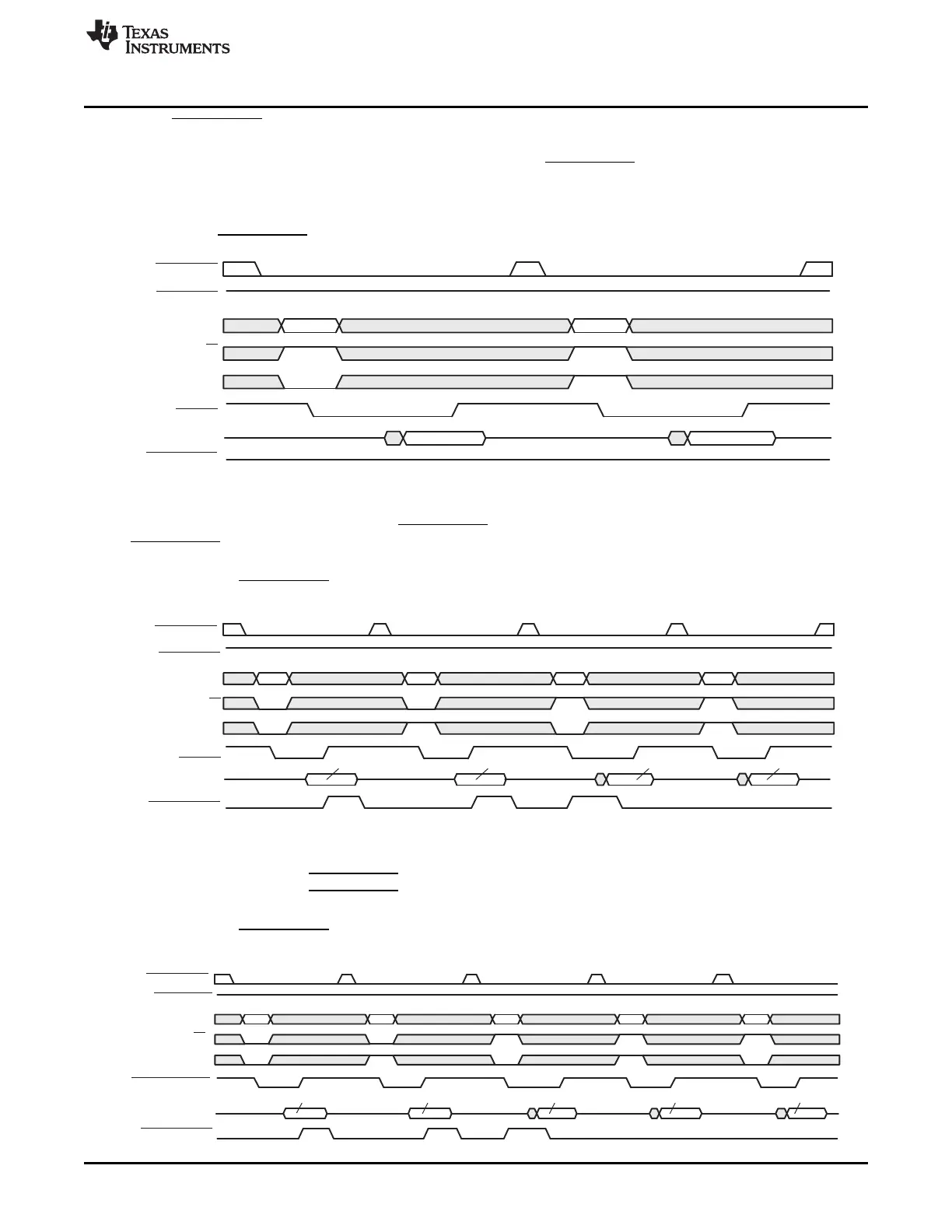

Figure 21-7 shows an HPIC (UHPI_HCNTL[1:0] = 00b) or HPIA (UHPI_HCNTL[1:0] = 10b) read cycle.

Neither an HPIC read cycle nor an HPIA read cycle causes UHPI_HRDY to go high. For this type of

access, the state of UHPI_HHWIL is ignored, so if a dual halfword access is performed, the same register

will be accessed twice.

Figure 21-7. UHPI_HRDY Behavior During an HPIC or HPIA Read Cycle in the Multiplexed Mode

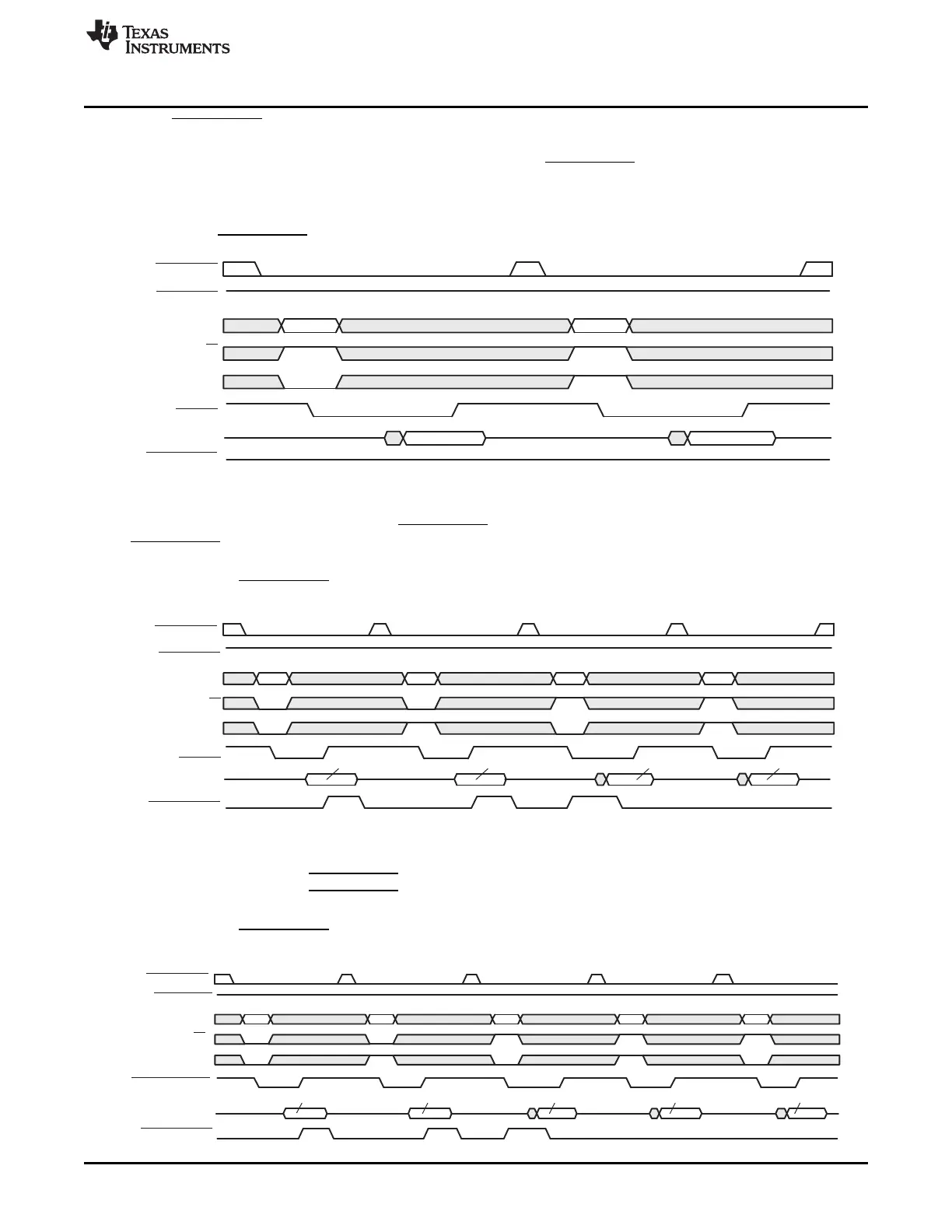

Figure 21-8 includes an HPID read cycle without autoincrementing. The host writes the memory address

during the HPIA (UHPI_HCNTL[1:0] = 10b) write cycle, and the host reads the data during the HPID

(UHPI_HCNTL[1:0] = 11b) read cycle. UHPI_HRDY goes high for each HPIA halfword access, but

UHPI_HRDY goes high for only the first halfword access in each HPID read cycle.

Figure 21-8. UHPI_HRDY Behavior During a Data Read Operation in the Multiplexed Mode

(Case 1: HPIA Write Cycle Followed by Nonautoincrement HPID Read Cycle)

Figure 21-9 includes an autoincrement HPID read cycle. The host writes the memory address while

asserting UHPI_HCNTL[1:0] = 10b and reads the data while asserting UHPI_HCNTL[1:0] = 01b. During

the first HPID read cycle, UHPI_HRDY goes high for only the first halfword access, and subsequent HPID

read cycles do not cause UHPI_HRDY to go high.

Figure 21-9. UHPI_HRDY Behavior During a Data Read Operation in the Multiplexed Mode

(Case 2: HPIA Write Cycle Followed by Autoincrement HPID Read Cycles)

Loading...

Loading...