Registers

www.ti.com

534

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

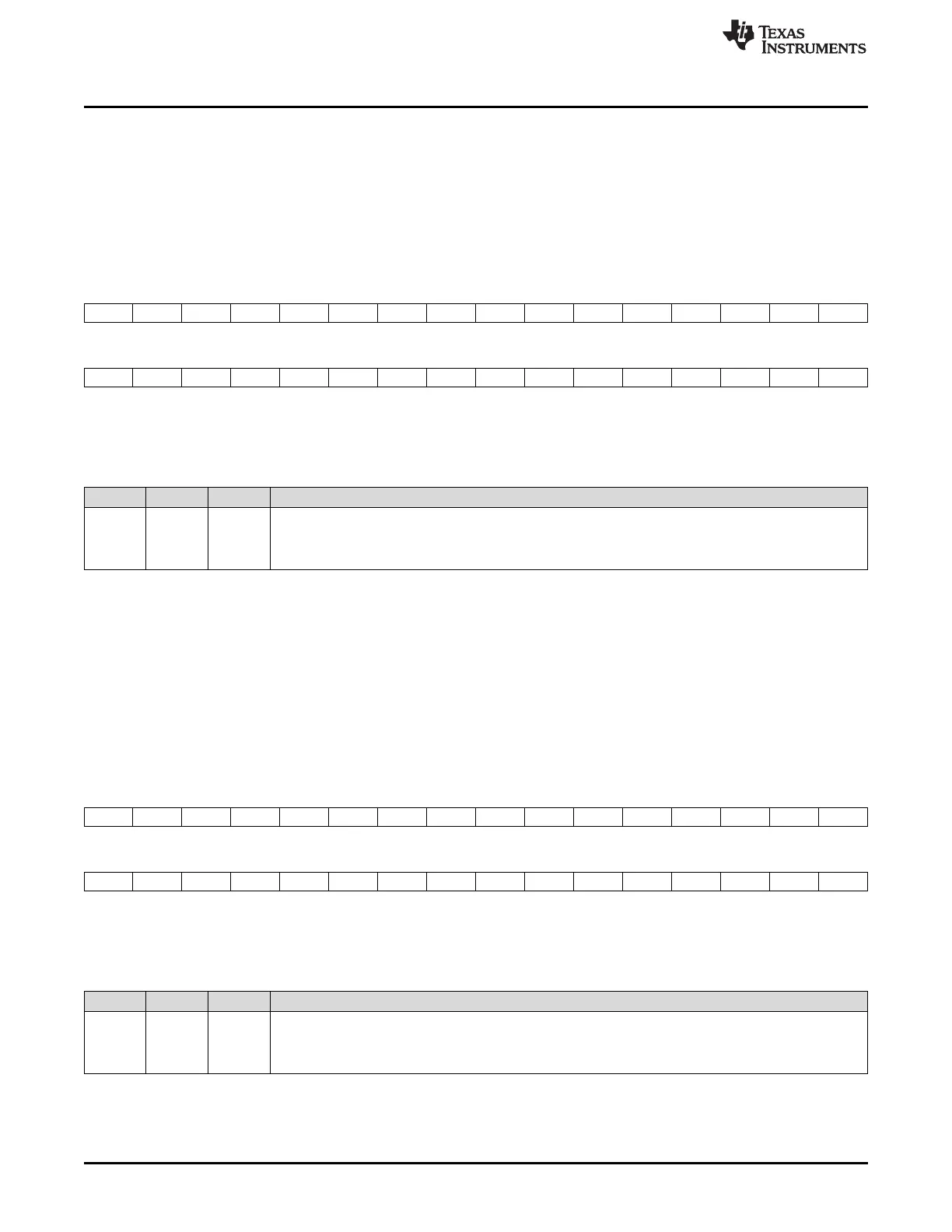

16.4.2.5.6 Event Enable Clear Register (EECR)

The event enable register (EER) cannot be modified by directly writing to it. The intent is to ease the

software burden for the case where multiple tasks are attempting to simultaneously modify these registers.

The event enable clear register (EECR) is used to disable events. Writes of 1 to the bits in EECR clear the

corresponding event bits in EER; writes of 0 have no effect.

The EECR is shown in Figure 16-66 and described in Table 16-45.

Figure 16-66. Event Enable Clear Register (EECR)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

E31 E30 E29 E28 E27 E26 E25 E24 E23 E22 E21 E20 E19 E18 E17 E16

W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

E15 E14 E13 E12 E11 E10 E9 E8 E7 E6 E5 E4 E3 E2 E1 E0

W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0

LEGEND: W = Write only; -n = value after reset

Table 16-45. Event Enable Clear Register (EECR) Field Descriptions

Bit Field Value Description

31-0 En Event enable clear for events 0-31.

0 No effect.

1 Event is disabled. Corresponding bit in the event enable register (EER) is cleared (En = 0).

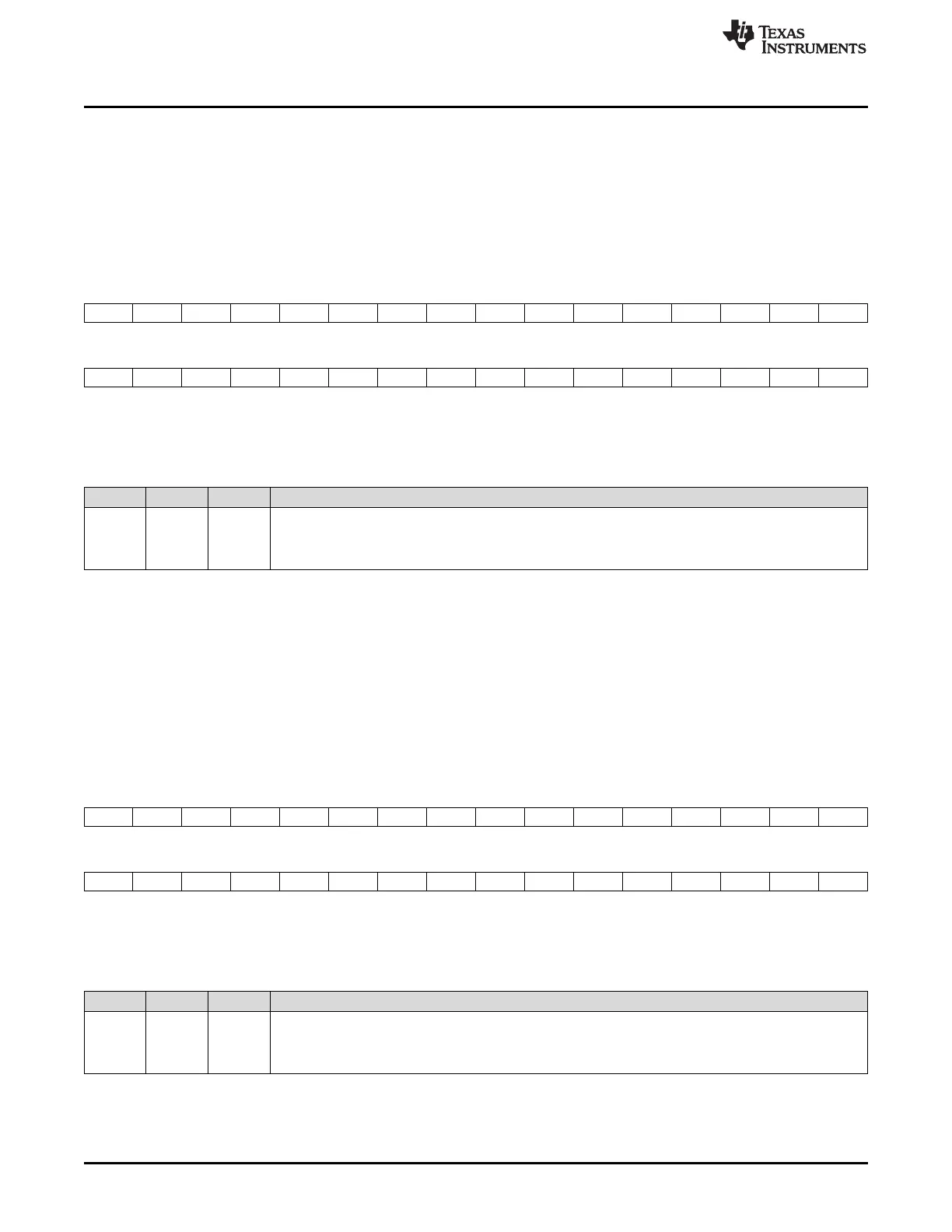

16.4.2.5.7 Event Enable Set Register (EESR)

The event enable register (EER) cannot be modified by directly writing to it. The intent is to ease the

software burden for the case where multiple tasks are attempting to simultaneously modify these registers.

The event enable set register (EESR) is used to enable events. Writes of 1 to the bits in EESR set the

corresponding event bits in EER; writes of 0 have no effect.

The EESR is shown in Figure 16-67 and described in Table 16-46.

Figure 16-67. Event Enable Set Register (EESR)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

E31 E30 E29 E28 E27 E26 E25 E24 E23 E22 E21 E20 E19 E18 E17 E16

W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

E15 E14 E13 E12 E11 E10 E9 E8 E7 E6 E5 E4 E3 E2 E1 E0

W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0

LEGEND: W = Write only; -n = value after reset

Table 16-46. Event Enable Set Register (EESR) Field Descriptions

Bit Field Value Description

31-0 En Event enable set for events 0-31.

0 No effect.

1 Event is enabled. Corresponding bit in the event enable register (EER) is set (En = 1).

Loading...

Loading...