www.ti.com

SYSCFG Registers

205

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

System Configuration (SYSCFG) Module

10.5.10.10 Pin Multiplexing Control 9 Register (PINMUX9)

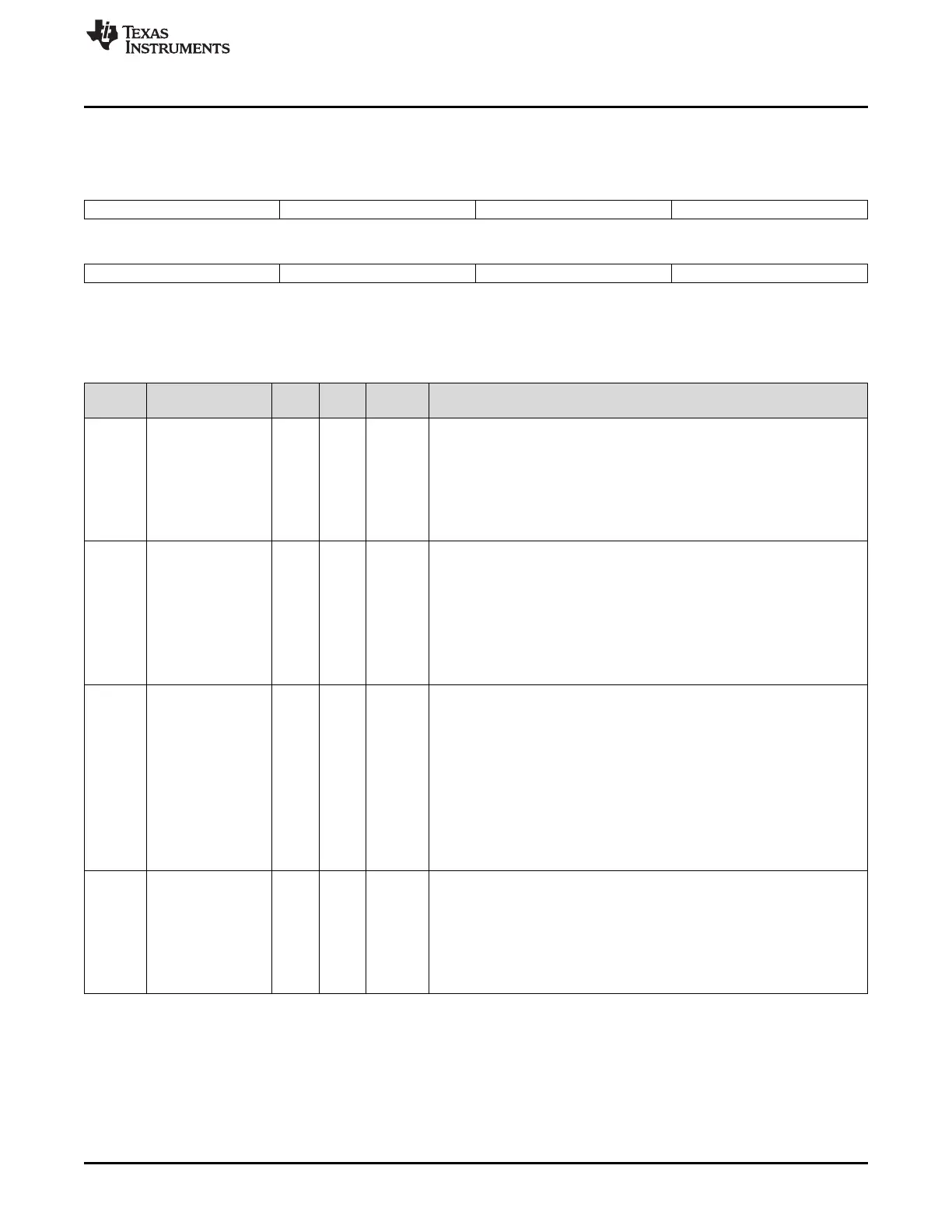

Figure 10-27. Pin Multiplexing Control 9 Register (PINMUX9)

31 28 27 24 23 20 19 16

PINMUX9_31_28 PINMUX9_27_24 PINMUX9_23_20 PINMUX9_19_16

R/W-0 R/W-0 R/W-0 R/W-0

15 12 11 8 7 4 3 0

PINMUX9_15_12 PINMUX9_11_8 PINMUX9_7_4 PINMUX9_3_0

R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

(1)

The ZKB ball package is only available on the C6747 DSP; this package is not supported on the C6745 DSP.

(2)

The PTP pin package is only available on the C6745 DSP; this package is not supported on the C6747 DSP.

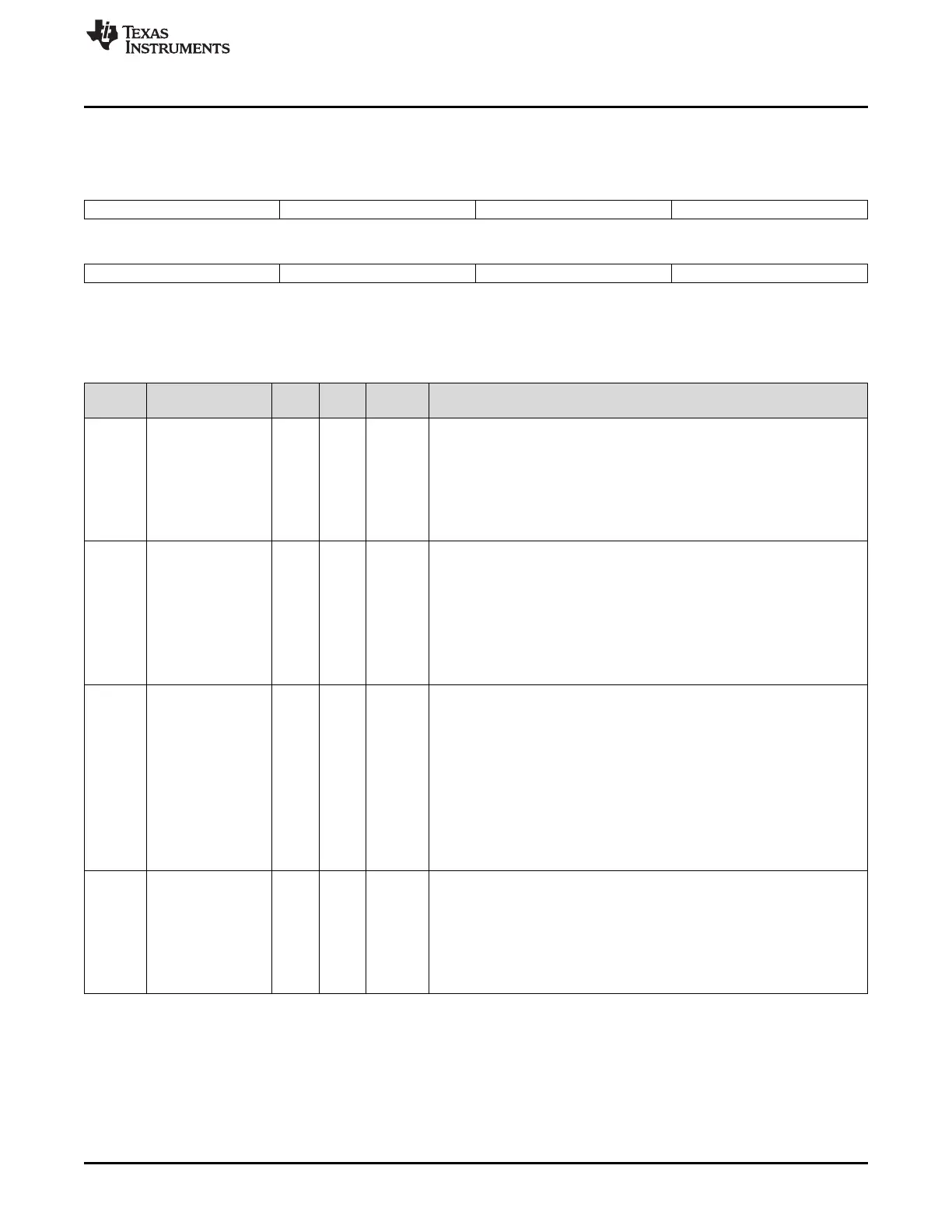

Table 10-31. Pin Multiplexing Control 9 Register (PINMUX9) Field Descriptions

Bit Field

ZKB

Ball

(1)

PTP

Pin

(2)

Value Description

31-28 PINMUX9_31_28 C4 131 AFSR0/GP3[12] Control

0 Pin is 3-stated.

1h Selects Function AFSR0

2h-7h Reserved

8h Selects Function GP3[12]

9h-Fh Reserved

27-24 PINMUX9_27_24 B4 130 ACLKR0/ECAP1/APWM1/GP2[15] Control

0 Pin is 3-stated.

1h Selects Function ACLKR0

2h Selects Function ECAP1/APWM1

3h-7h Reserved

8h Selects Function GP2[15]

9h-Fh Reserved

23-20 PINMUX9_23_20 A4 129 AHCLKR0/RMII_MHZ_50_CLK/GP2[14]/BOOT[11] Control

0 Pin is 3-stated. Enables sourcing of the EMAC 50 MHz reference clock from

an external source on the RMII_MHZ_50_CLK pin.

1h Selects Function AHCLKR0

2h Selects Function RMII_MHZ_50_CLK. Enables sourcing of the EMAC

50 MHz reference clock from PLL SYSCLK7. Also, SYSCLK7 is driven out on

the RMII_MHZ_50_CLK pin.

3h-7h Reserved

8h Selects Function GP2[14]

9h-Fh Reserved

19-16 PINMUX9_19_16 D5 127 AFSX0/GP2[13]/BOOT[10] Control

0 Pin is 3-stated.

1h Selects Function AFSX0

2h-7h Reserved

8h Selects Function GP2[13]

9h-Fh Reserved

Loading...

Loading...