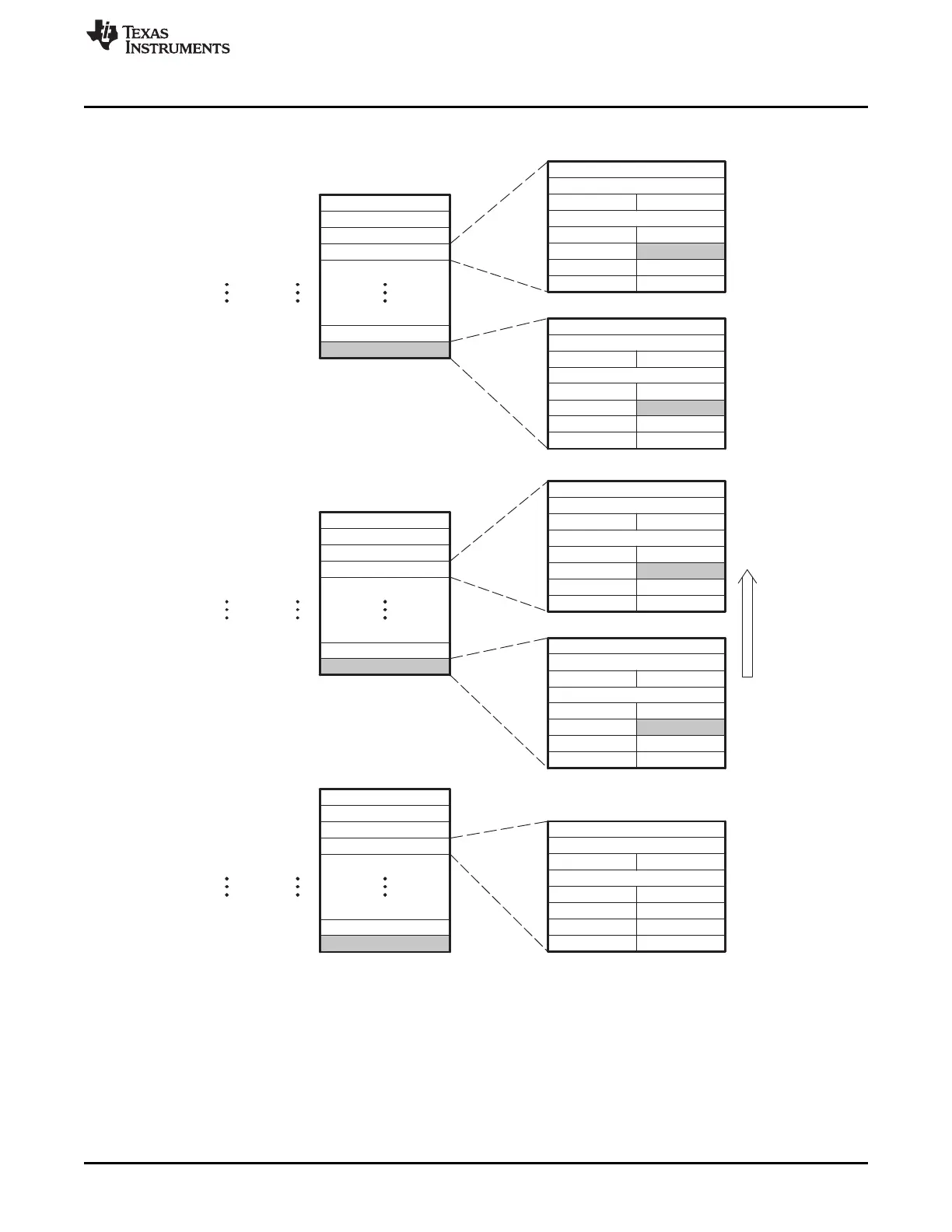

Parameter set 0

PaRAM

Set

#

Byte

address

001C0 4000h

01C0 4020h 1 Parameter set 1

01C0 4040h 2 Parameter set 2

01C0 4060h 3 Parameter set 3

01C0 4FC0h

01C0 4FE0h

126

127 Parameter set 127

Parameter set 126

OPT X

SRC X

BCNT X ACNT X

DST X

SRCBIDX XDSTBIDX X

Link X=4FE0hBCNTRLD X

CCNT X

SRCCIDX XDSTCIDX X

Rsvd

PaRAM set 3

PaRAM set 127

01C0 4FC0h

01C0 4FE0h

126

127

Parameter set 126

Parameter set 127

Parameter set 0001C0 4000h

01C0 4040h

01C0 4060h

01C0 4020h

2

3

1 Parameter set 1

Parameter set 2

Parameter set 3

Byte

address

Set

#

PaRAM

PaRAM set 3

(a) At initialization

(b) After completion of PaRAM set 3

(link update)

Link

update

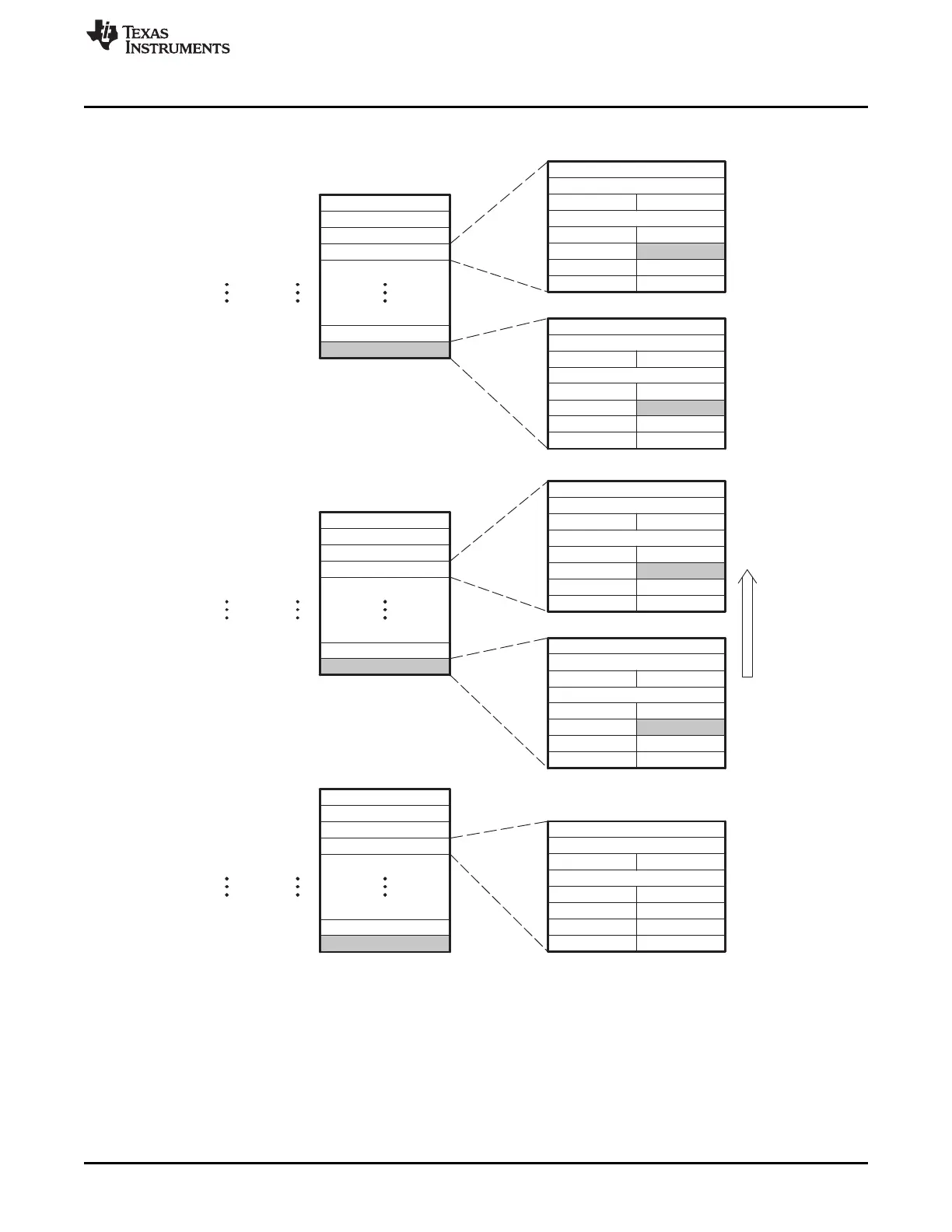

01C0 4FC0h 126 Parameter set 126

Parameter set 0001C0 4000h

01C0 4040h

01C0 4060h

01C0 4020h

2

3

1 Parameter set 1

Parameter set 2

Parameter set 3

Byte

address

Set

#

PaRAM

0h

0h

Link=FFFFh

0h

0h

0h

0h

0h

0h

0h

0h

0h

PaRAM set 3 (Null PaRAM set)

0h

1CA0 4FE0h 127 Parameter set 127

(c) After completion of PaRAM set 127

(link to null set)

OPT Y

SRC Y

BCNT Y ACNT Y

DST Y

SRCBIDX YDSTBIDX Y

Link Y=FFFFhBCNTRLD Y

CCNT Y

SRCCIDX YDSTCIDX Y

Rsvd

OPT Y

SRC Y

BCNT Y ACNT Y

DST Y

SRCBIDX YDSTBIDX Y

Link Y=FFFFhBCNTRLD Y

CCNT Y

SRCCIDX YDSTCIDX Y

Rsvd

PaRAM set 127

OPT Y

SRC Y

BCNT Y ACNT Y

DST Y

SRCBIDX YDSTBIDX Y

Link Y=FFFFhBCNTRLD Y

CCNT Y

SRCCIDX YDSTCIDX Y

Rsvd

www.ti.com

Architecture

455

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

Figure 16-8. Linked Transfer Example

Loading...

Loading...