Registers

www.ti.com

682

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

EMAC/MDIO Module

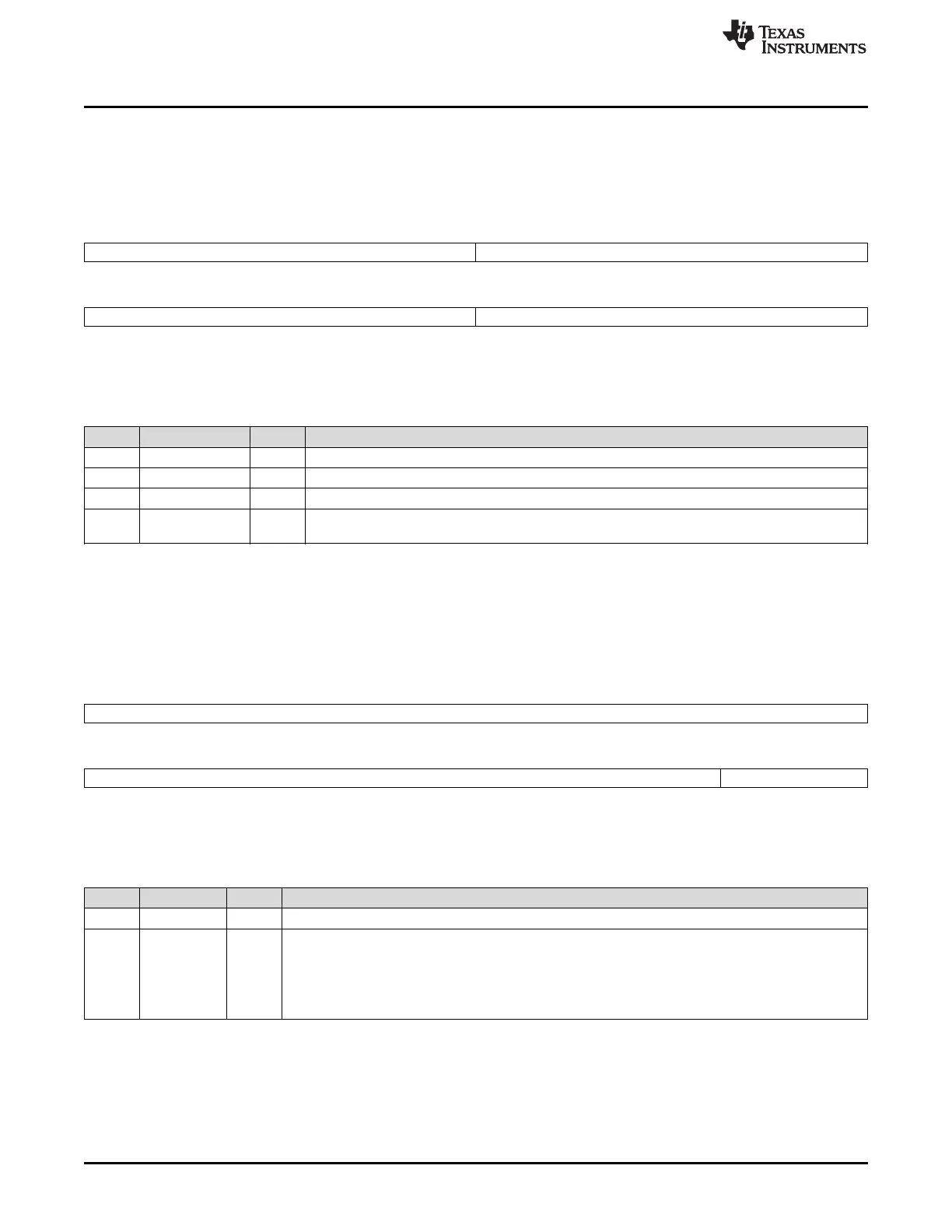

17.3.3.44 MAC Address High Bytes Register (MACADDRHI)

The MAC address high bytes register (MACADDRHI) is shown in Figure 17-82 and described in

Table 17-81.

Figure 17-82. MAC Address High Bytes Register (MACADDRHI)

31 24 23 16

MACADDR2 MACADDR3

R/W-x R/W-x

15 8 7 0

MACADDR4 MACADDR5

R/W-x R/W-x

LEGEND: R/W = Read/Write; -x = value is indeterminate after reset

Table 17-81. MAC Address High Bytes Register (MACADDRHI) Field Descriptions

Bit Field Value Description

31-24 MACADDR2 0-FFh MAC source address bits 23-16 (byte 2)

23-16 MACADDR3 0-FFh MAC source address bits 31-24 (byte 3)

15-8 MACADDR4 0-FFh MAC source address bits 39-32 (byte 4)

7-0 MACADDR5 0-FFh MAC source address bits 47-40 (byte 5). Bit 40 is the group bit. It is forced to 0 and read as 0.

Therefore, only unicast addresses are represented in the address table.

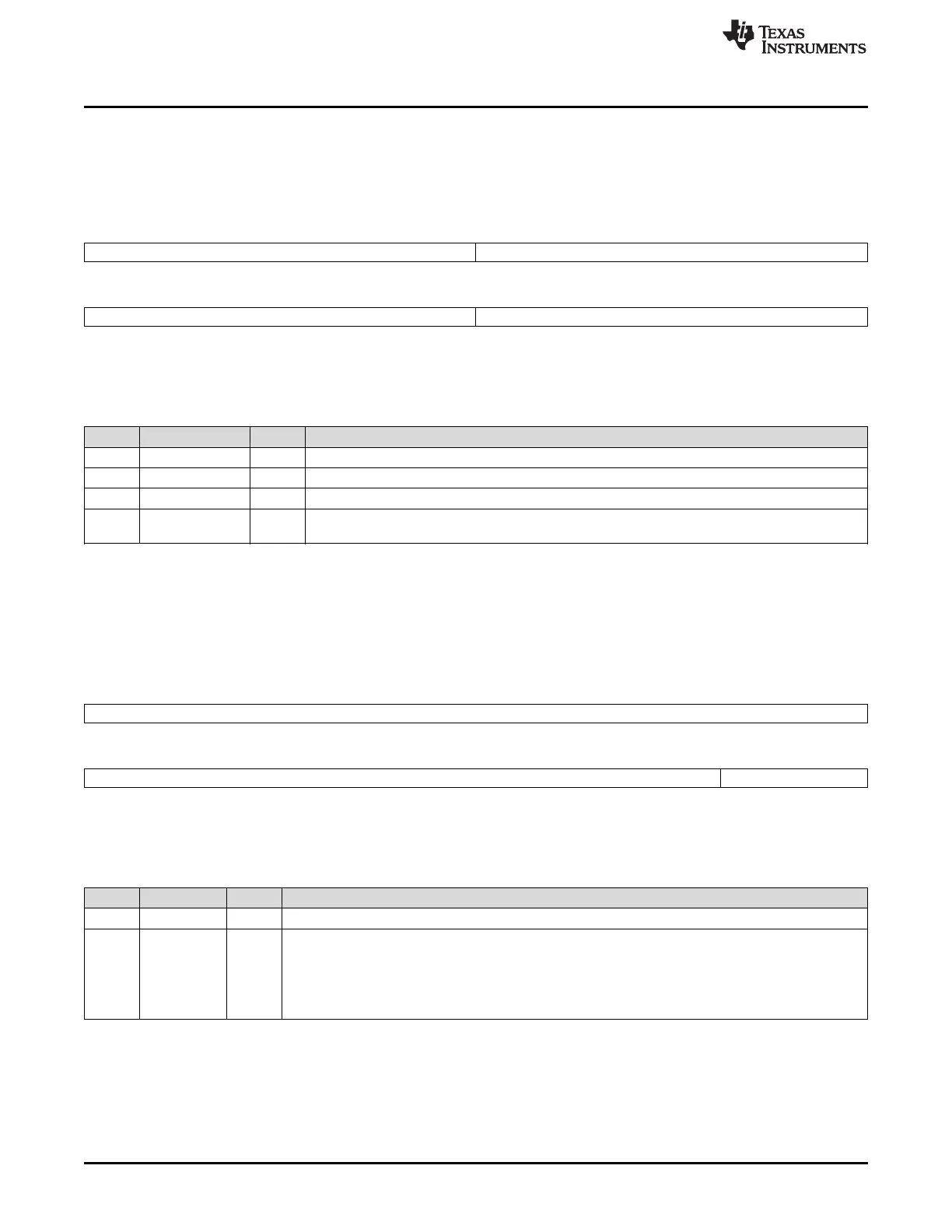

17.3.3.45 MAC Index Register (MACINDEX)

The MAC index register (MACINDEX) is shown in Figure 17-83 and described in Table 17-82.

Figure 17-83. MAC Index Register (MACINDEX)

31 16

Reserved

R-0

15 3 2 0

Reserved MACINDEX

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 17-82. MAC Index Register (MACINDEX) Field Descriptions

Bit Field Value Description

31-3 Reserved 0 Reserved

2-0 MACINDEX 0-7h MAC address index. All eight addresses share the upper 40 bits. Only the lower byte is unique for each

address. An address is written by first writing the address number (channel) into the MACINDEX

register. The upper 32 bits of the address are then written to the MACADDRHI register, which is

followed by writing the lower 16 bits of the address to the MACADDRLO register. Since all eight

addresses share the upper 40 bits of the address, the MACADDRHI register only needs to be written

the first time.

Loading...

Loading...