www.ti.com

Registers

541

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

16.4.2.7 QDMA Channel Registers

The following registers pertain to the 8 QDMA channels. The 8 QDMA channels consist of registers (with

the exception of QDMAQNUM) that each have 8 bits and the bit position of each register matches the

QDMA channel number.

The QDMA channel registers are accessible via read/writes to the global address range. They are also

accessible via read/writes to the shadow address range. The read/write ability to the registers in the

shadow region is controlled by the QDMA region access registers (QRAEm). These registers are

described in Section 16.4.2.3.2 and the details for shadow region/global region usage is explained in

Section 16.2.7.

16.4.2.7.1 QDMA Event Register (QER)

The QDMA event register (QER) channel n bit is set (En = 1) when the CPU or any EDMA programmer

(including EDMA3) performs a write to the trigger word (using the QDMA channel n mapping register

(QCHMAPn)) in the PaRAM entry associated with QDMA channel n (which is also programmed using

QCHMAPn). The En bit is also set when the EDMA3CC performs a link update on a PaRAM address that

matches the QCHMAPn settings. The QDMA event is latched only if the QDMA event enable register

(QEER) channel n bit is also enabled (QEER.En = 1). Once a bit is set in QER, then the corresponding

QDMA event (auto-trigger) is evaluated by the EDMA3CC logic for an associated transfer request

submission to the transfer controllers.

The setting of an event is a higher priority relative to clear operations (via hardware). If set and clear

conditions occur concurrently, the set condition wins. If the event was previously set, then the QDMA

event missed register (QEMR) would be set because an event is lost. If the event was previously clear,

then the event remains set and is prioritized for submission to the event queues.

The set bits in QER are only cleared when the transfer request associated with the corresponding

channels has been processed by the EDMA3CC and submitted to the transfer controller. If the En bit is

already set and a QDMA event for the same QDMA channel occurs prior to the original being cleared,

then the second missed event is latched in QEMR (En =1).

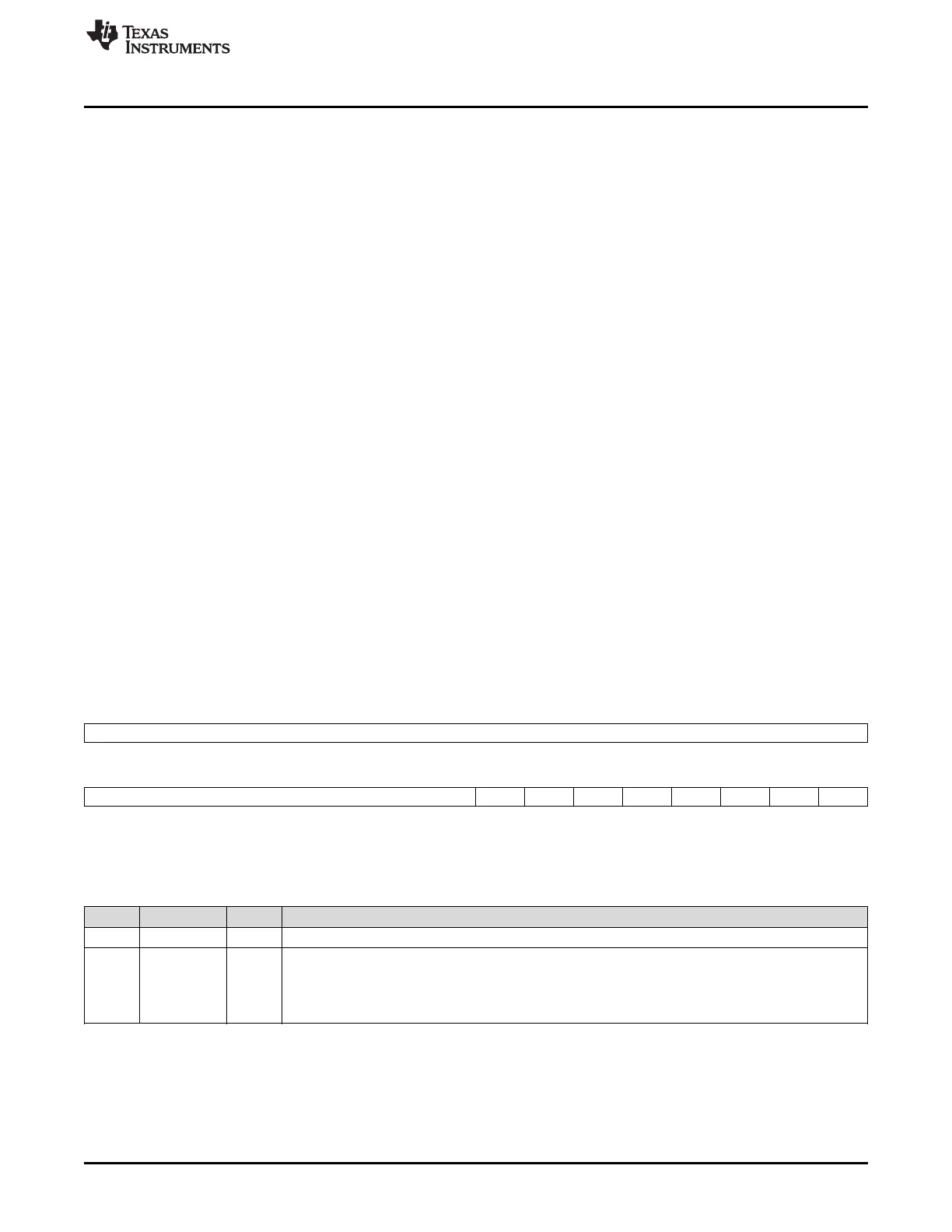

The QER is shown in Figure 16-76 and described in Table 16-55.

Figure 16-76. QDMA Event Register (QER)

31 16

Reserved

R-0

15 8 7 6 5 4 3 2 1 0

Reserved E7 E6 E5 E4 E3 E2 E1 E0

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

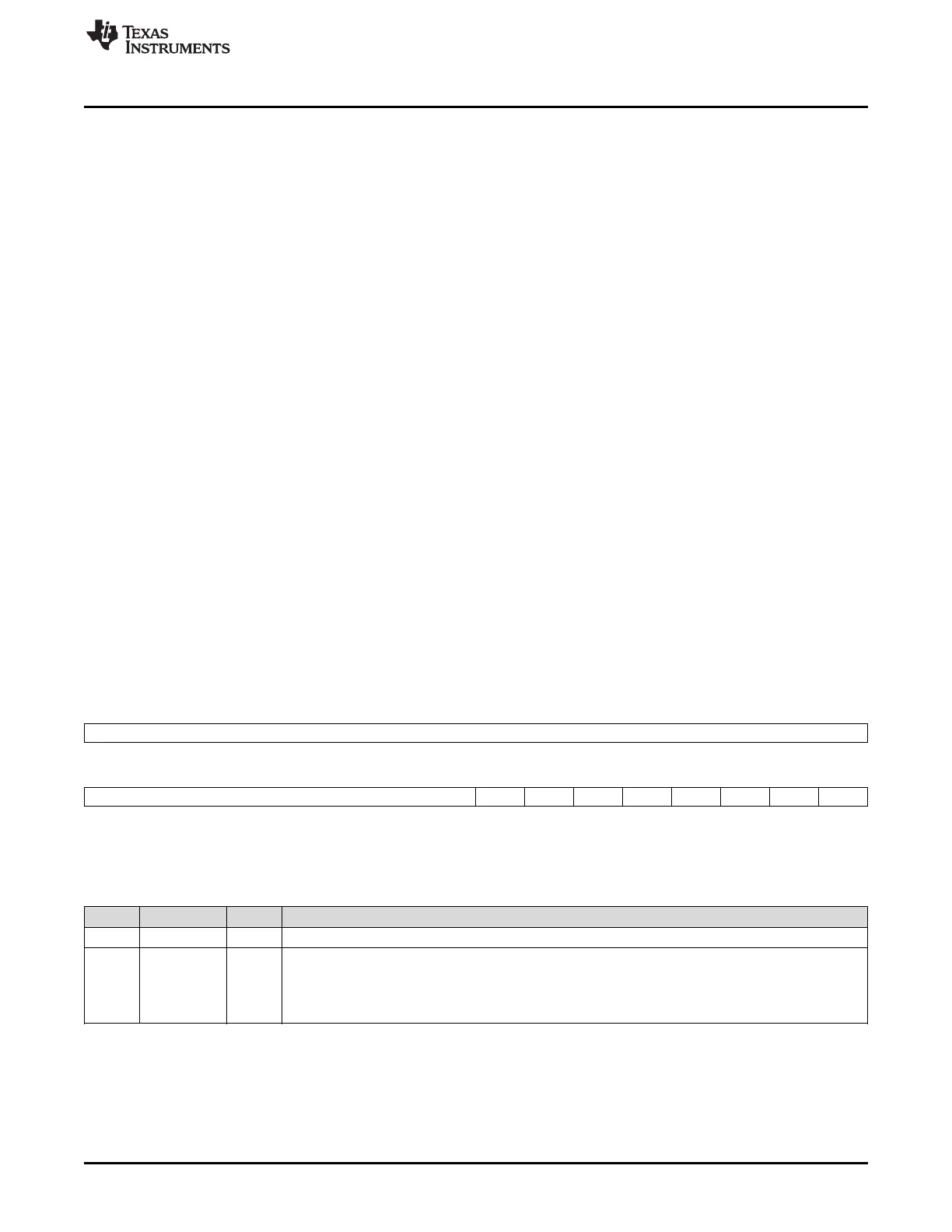

Table 16-55. QDMA Event Register (QER) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved

7-0 En QDMA event for channels 0-7.

0 No effect.

1 Corresponding QDMA event is prioritized versus other pending DMA/QDMA events for submission to

the EDMA3TC.

Loading...

Loading...