Registers

www.ti.com

656

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

EMAC/MDIO Module

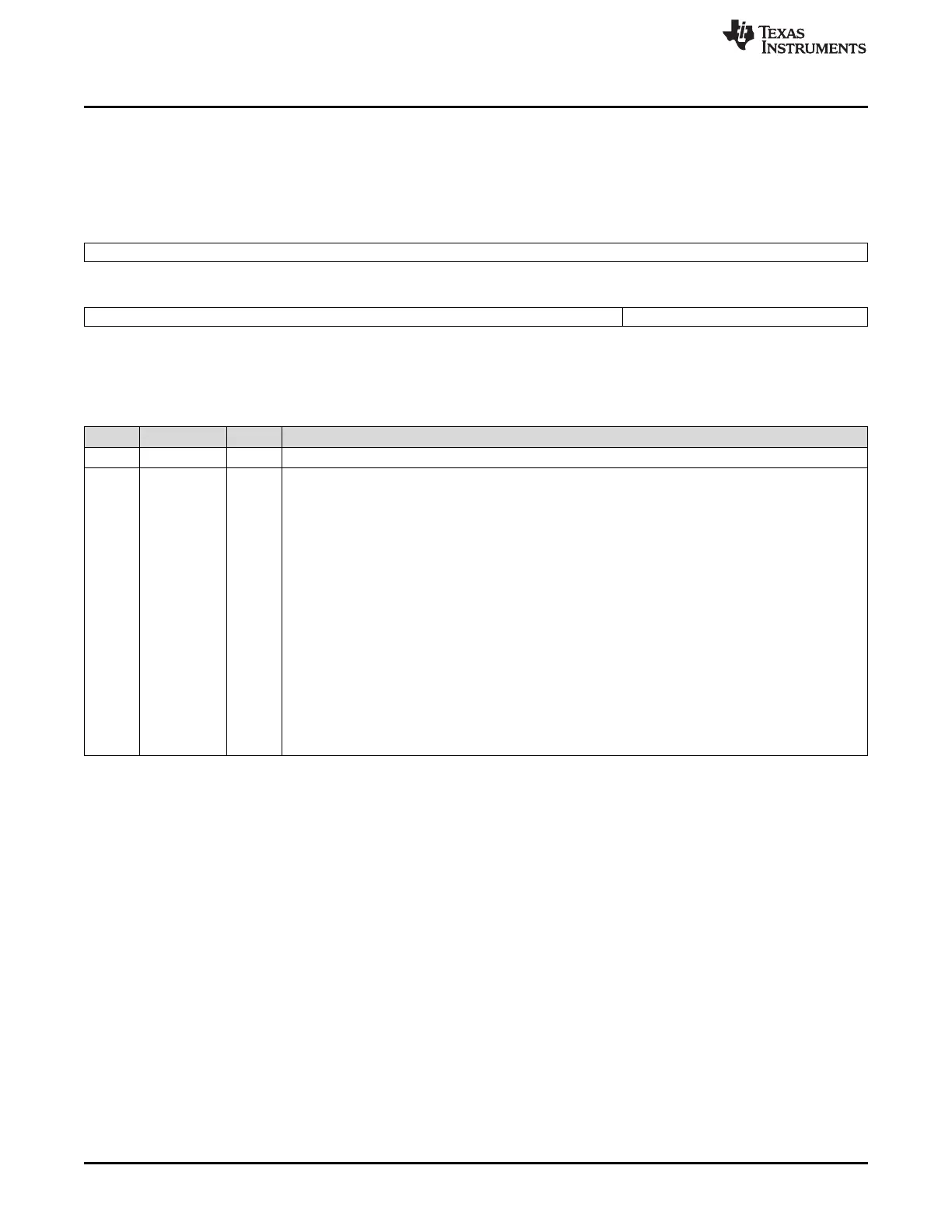

17.3.3.12 MAC End Of Interrupt Vector Register (MACEOIVECTOR)

The MAC end of interrupt vector register (MACEOIVECTOR) is shown in Figure 17-50 and described in

Table 17-49.

Figure 17-50. MAC End Of Interrupt Vector Register (MACEOIVECTOR)

31 16

Reserved

R-0

15 5 4 0

Reserved INTVECT

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

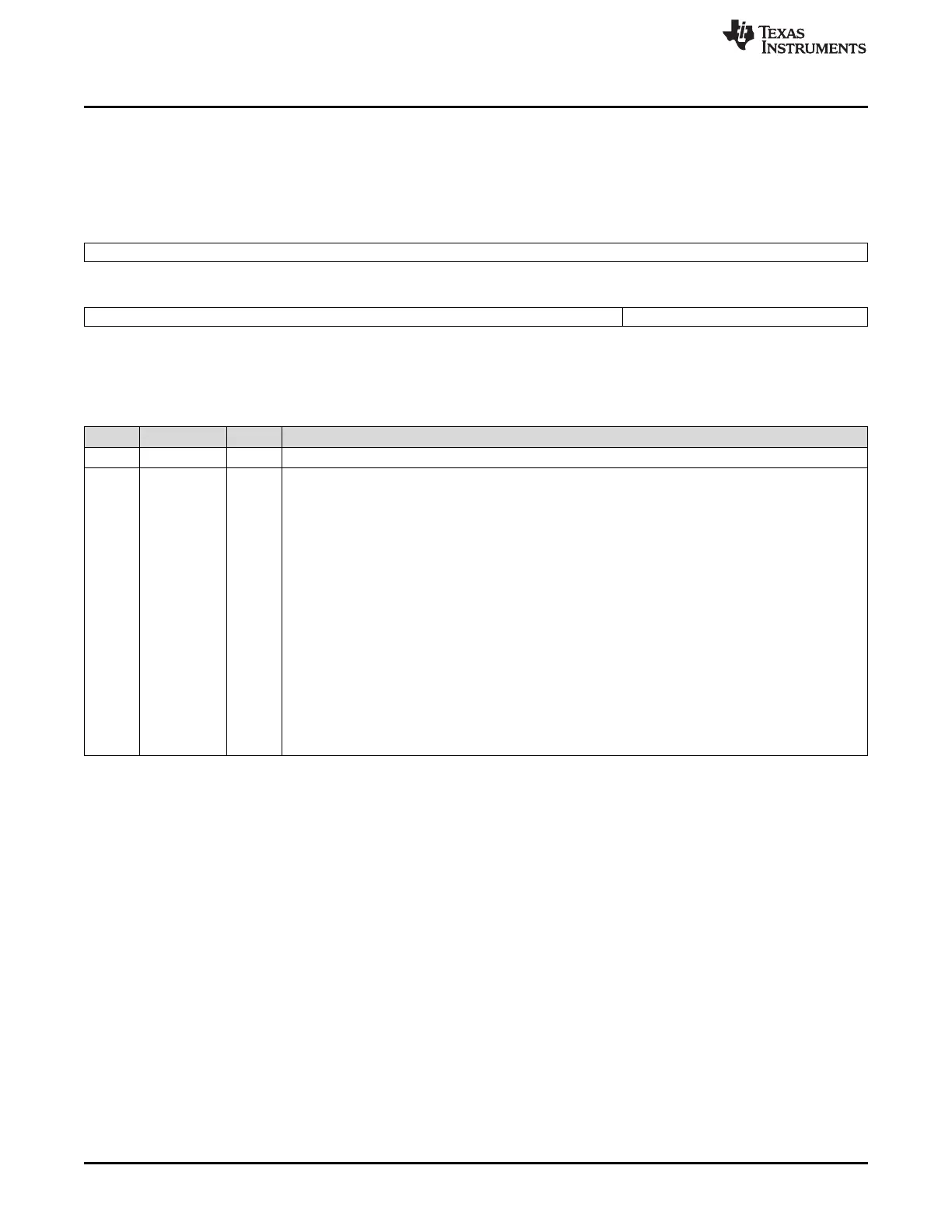

Table 17-49. MAC End Of Interrupt Vector Register (MACEOIVECTOR) Field Descriptions

Bit Field Value Description

31-5 Reserved 0 Reserved

4-0 INTVECT 0-1Fh Acknowledge EMAC Control Module Interrupts

0h Acknowledge C0RXTHRESH Interrupt

1h Acknowledge C0RX Interrupt

2h Acknowledge C0TX Interrupt

3h Acknowledge C0MISC Interrupt (STATPEND, HOSTPEND, MDIO LINKINT0, MDIO USERINT0)

4h Acknowledge C1RXTHRESH Interrupt

5h Acknowledge C1RX Interrupt

6h Acknowledge C1TX Interrupt

7h Acknowledge C1MISC Interrupt (STATPEND, HOSTPEND, MDIO LINKINT0, MDIO USERINT0)

8h Acknowledge C2RXTHRESH Interrupt

9h Acknowledge C2RX Interrupt

Ah Acknowledge C2TX Interrupt

Bh Acknowledge C2MISC Interrupt (STATPEND, HOSTPEND, MDIO LINKINT0, MDIO USERINT0)

Ch-1Fh Reserved

Loading...

Loading...