Registers

www.ti.com

514

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

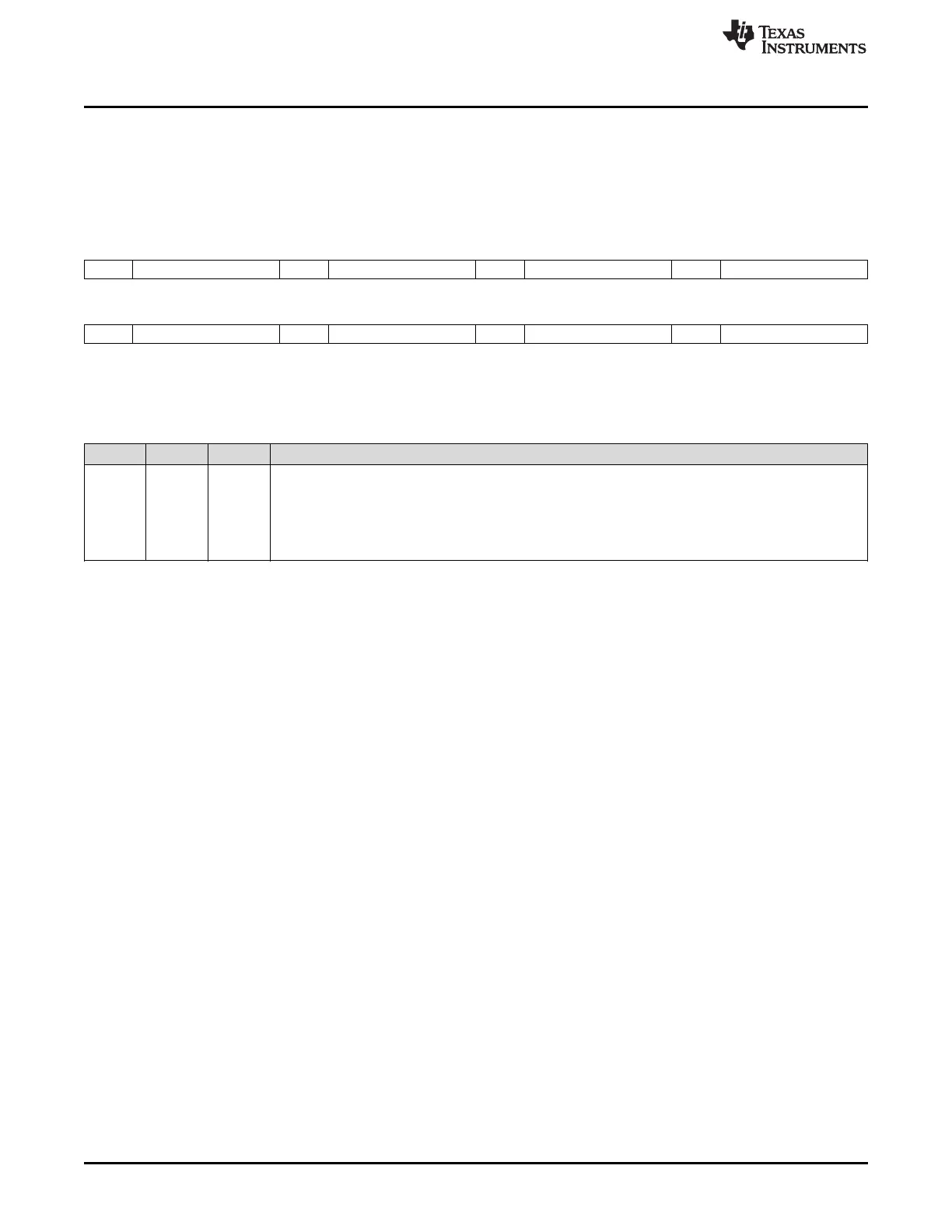

16.4.2.1.5 QDMA Channel Queue Number Register (QDMAQNUM)

The QDMA channel queue number register (QDMAQNUM) is used to program all the QDMA channels in

the EDMA3CC to submit the associated QDMA event to any of the event queues in the EDMA3CC. The

QDMAQNUM is shown in Figure 16-47 and described in Table 16-26.

Figure 16-47. QDMA Channel Queue Number Register (QDMAQNUM)

31 30 28 27 26 24 23 22 20 19 18 16

Rsvd E7 Rsvd E6 Rsvd E5 Rsvd E4

R-0 R/W-0 R-0 R/W-0 R-0 R/W-0 R-0 R/W-0

15 14 12 11 10 8 7 6 4 3 2 0

Rsvd E3 Rsvd E2 Rsvd E1 Rsvd E0

R-0 R/W-0 R-0 R/W-0 R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

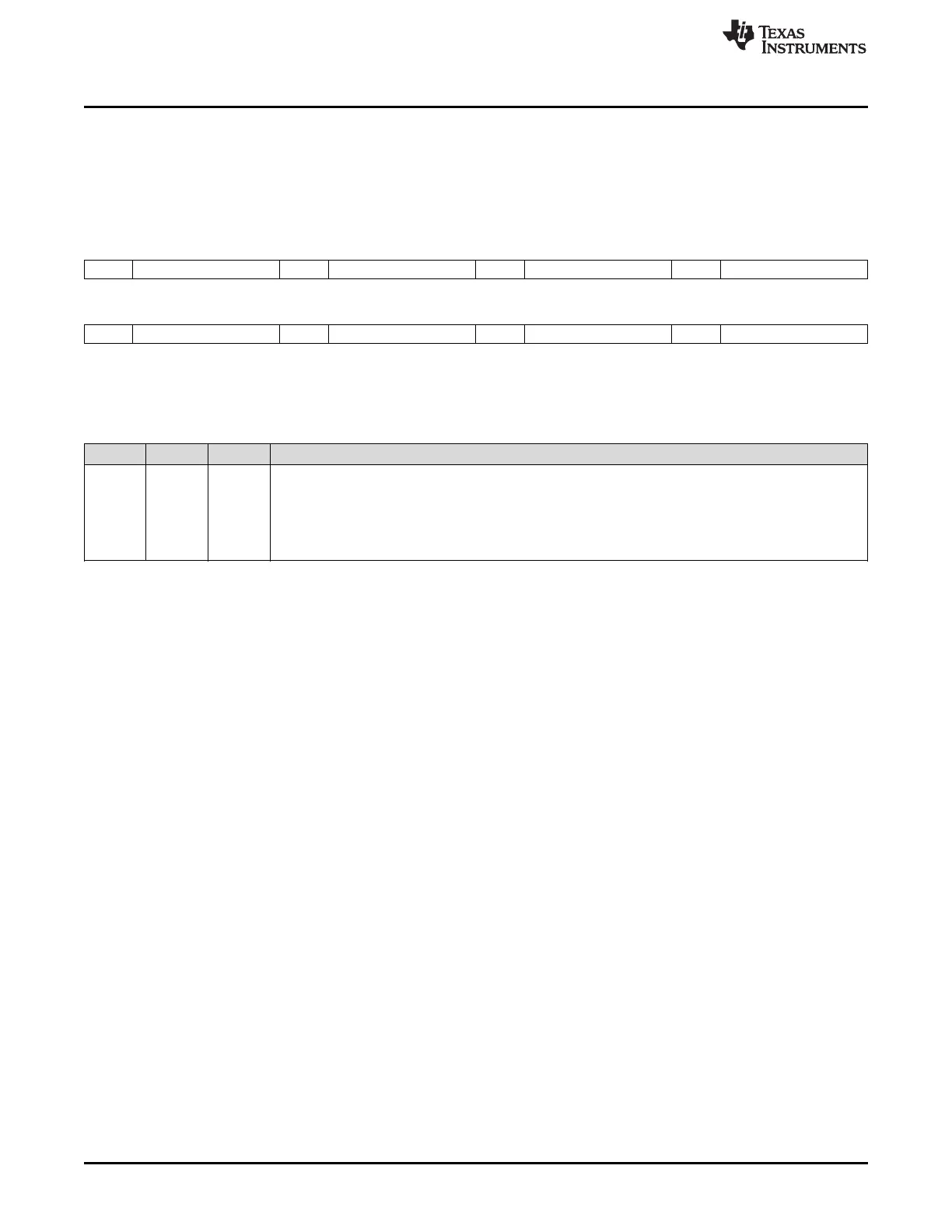

Table 16-26. QDMA Channel Queue Number Register (QDMAQNUM) Field Descriptions

Bit Field Value Description

31-0 En 0-7h QDMA queue number. Contains the event queue number to be used for the corresponding QDMA

channel.

0 Event n is queued on Q0.

1h Event n is queued on Q1.

2h-7h Reserved

16.4.2.1.6 Queue Priority Register (QUEPRI)

On previous architectures, the EDMA3TC priority was controlled by the queue priority register (QUEPRI)

in the EDMA3CC memory-map. However for this device, the priority control for the transfer controllers is

controlled by the chip-level registers in the System Configuration Module. You should use the chip-level

registers and not QUEPRI to configure the TC priority.

Loading...

Loading...