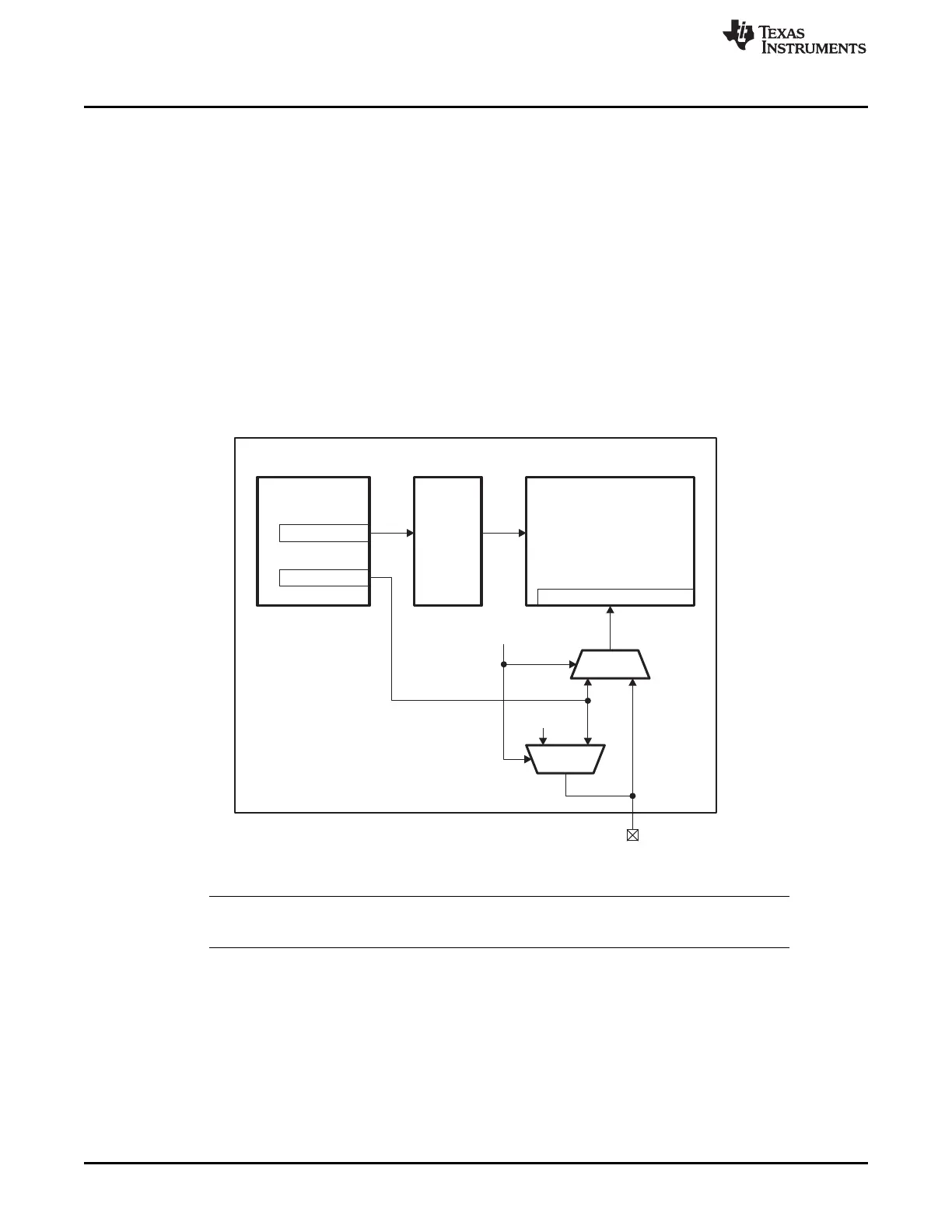

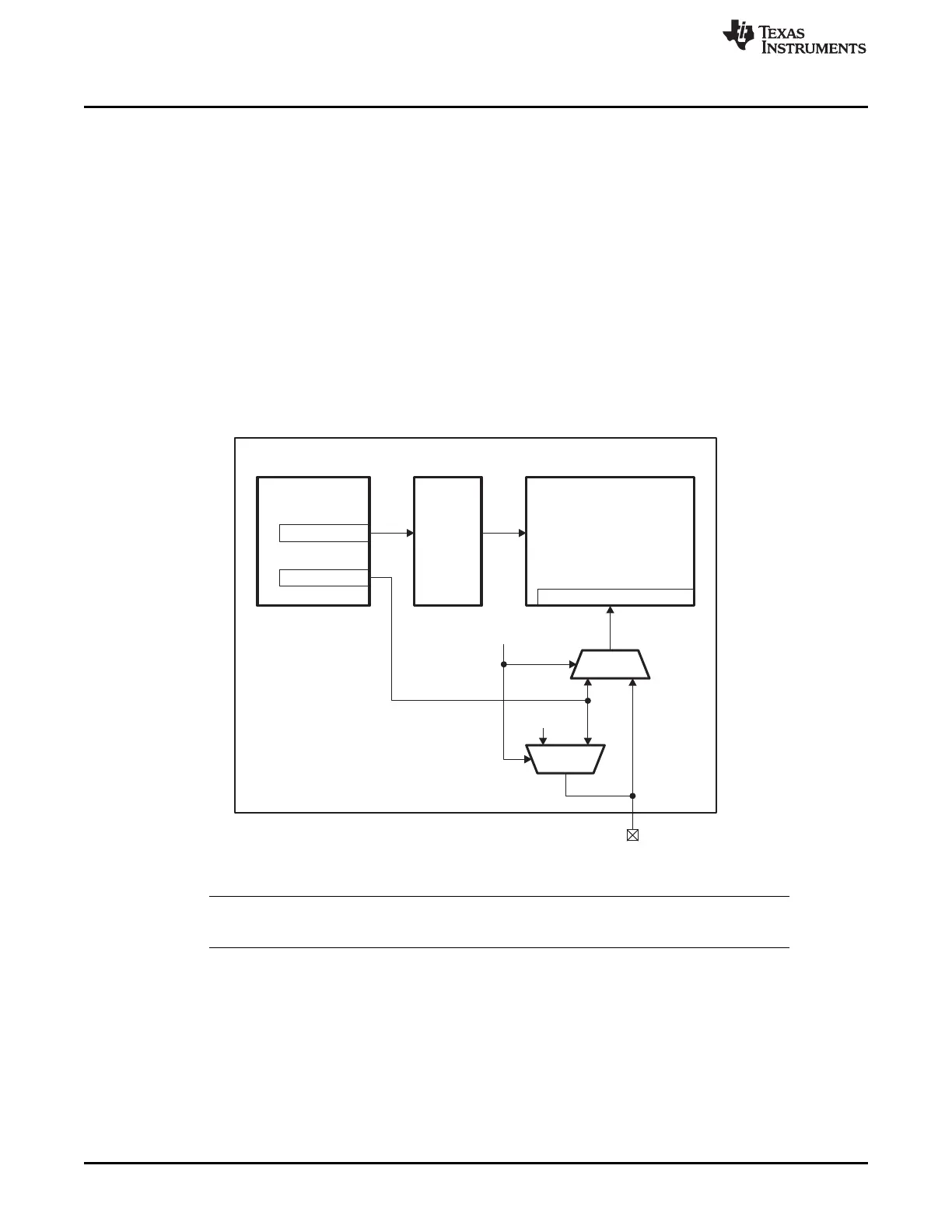

SYSCLK4

SYSCLK7

PLL Controller

LPSC

EMAC

0010 0000

PINMUX9[23:20]

RMII_MHZ_50_CLK

Signal

50MHzReferenceClock

OnChip

0000 0010

3-State

Peripheral Clocking

www.ti.com

112

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Device Clocking

6.3.4 EMAC Clocking

The EMAC module sources its peripheral bus interface reference clock from SYSCLK4 that is at a fixed

ratio of the CPU clock. The external clock requirement for EMAC varies with the interface used. When the

MII interface is active, the MII_TXCLK and MII_RXCLK signals must be provided from an external source.

When the RMII interface is active, the RMII 50 MHz reference clock is sourced either from an external

clock on the RMII_MHZ_50_CLK pin or from SYSCLK7 (as shown in Figure 6-5). The PINMUX9_23_20

bits in the pin multiplexing control 9 register (PINMUX9) of the System Configuration Module control this

clock selection:

• PINMUX9_23_20 = 0: enables sourcing of the 50 MHz reference clock from an external source on the

RMII_MHZ_50_CLK pin.

• PINMUX9_23_20 = 2h: enables sourcing of the 50 MHz reference clock from SYSCLK7. Also,

SYSCLK7 is driven out on the RMII_MHZ_50_CLK pin.

Table 6-7 shows example PLL register settings and the resulting SYSCLK7 frequencies based on the

OSCIN reference clock frequency of 25 MHz.

Figure 6-5. EMAC Clocking Diagram

NOTE: The SYSCLK7 output clock does not meet the RMII reference clock specification of

50 MHz +/-50 ppm.

Loading...

Loading...