Registers

www.ti.com

760

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface A (EMIFA)

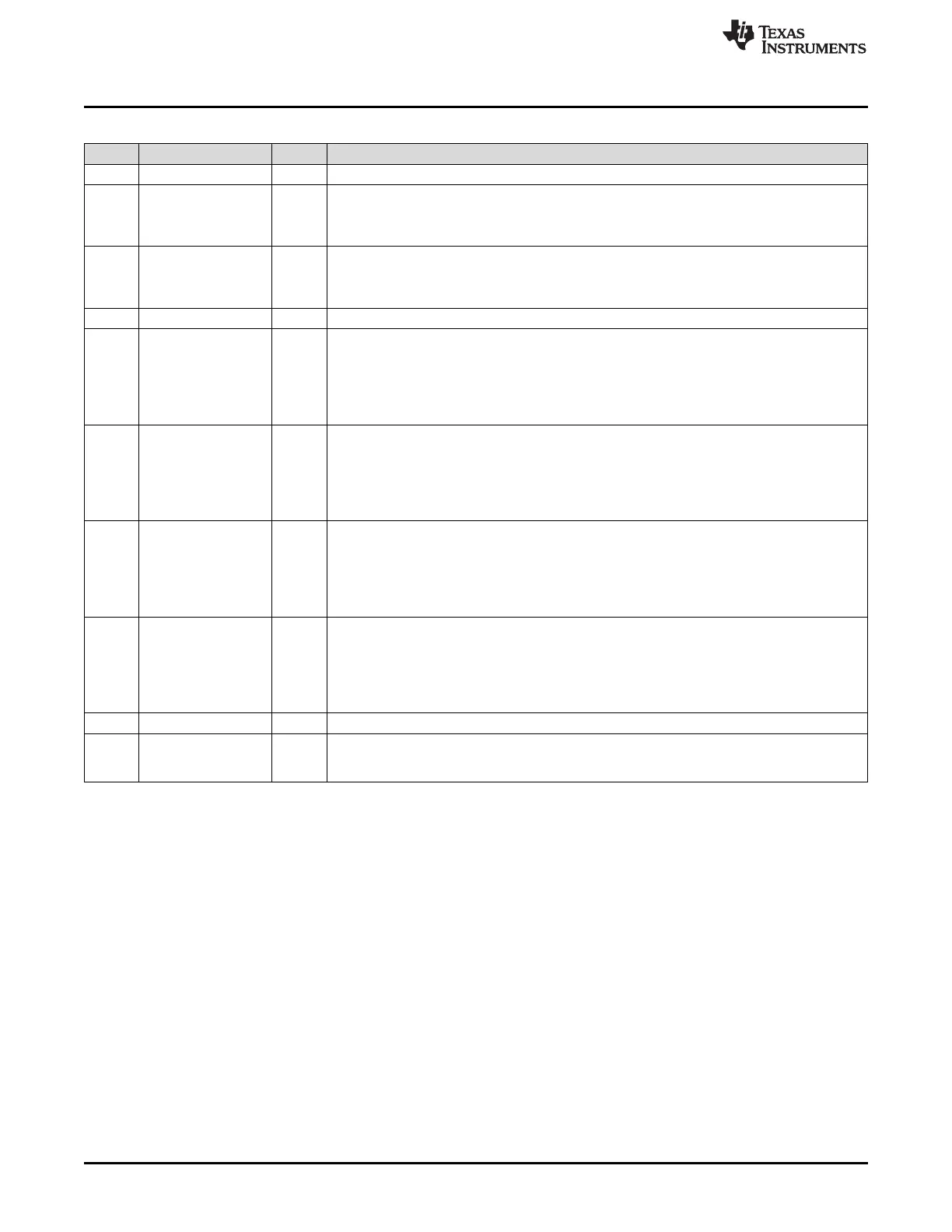

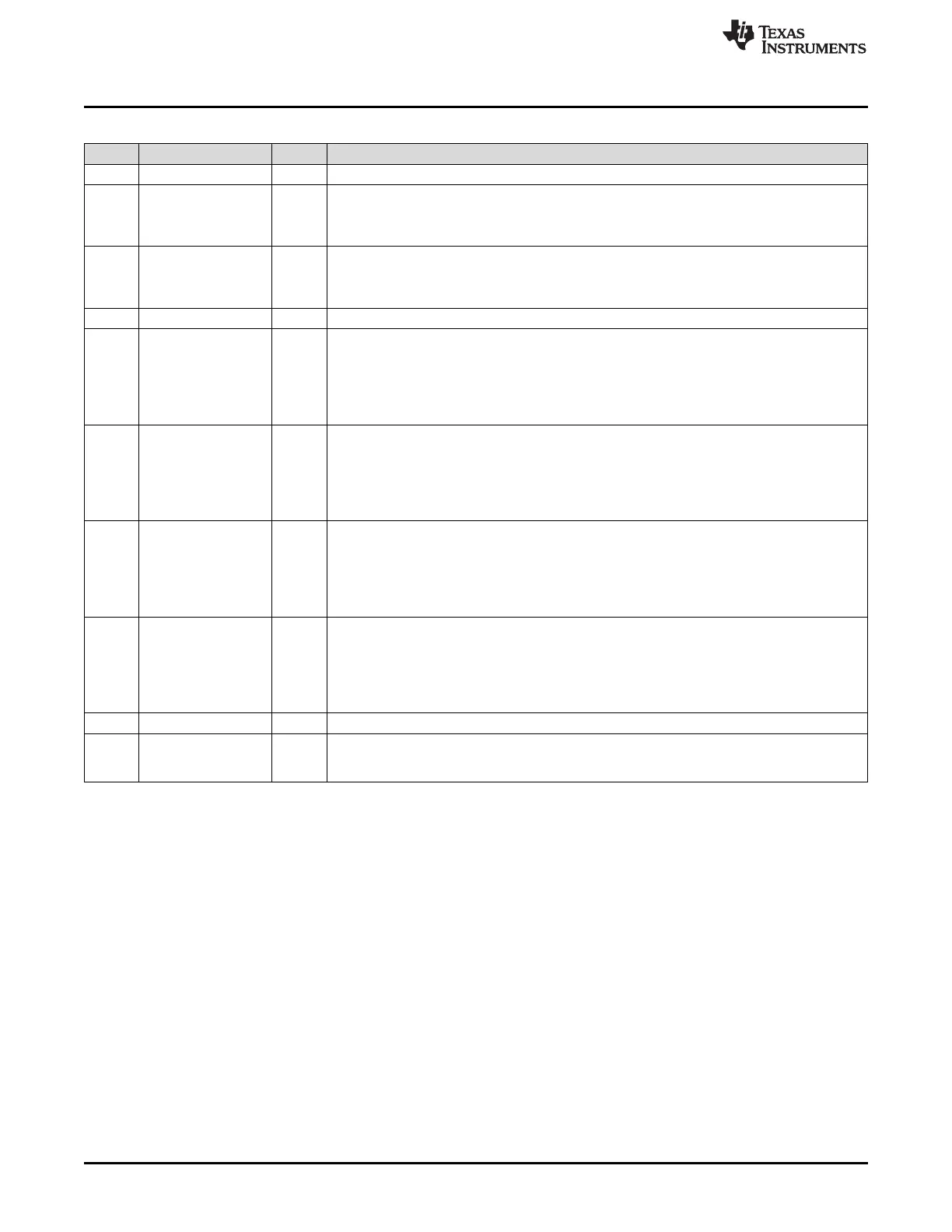

Table 18-50. Asynchronous Wait Cycle Configuration Register (AWCCR) Field Descriptions

Bit Field Value Description

31-30 Reserved 0 Reserved

29 WP1 EMA_WAIT[1] polarity bit. This bit defines the polarity of the EMA_WAIT[1] pin.

0 Insert wait cycles if EMA_WAIT[1] pin is low.

1 Insert wait cycles if EMA_WAIT[1] pin is high.

28 WP0 EMA_WAIT[0] polarity bit. This bit defines the polarity of the EMA_WAIT[0] pin.

0 Insert wait cycles if EMA_WAIT[0] pin is low.

1 Insert wait cycles if EMA_WAIT[0] pin is high.

27-24 Reserved 0 Reserved

23-22 CS5_WAIT 0-3h Chip Select 5 WAIT signal selection. This signal determines which EMA_WAIT[n] signal will be

used for memory accesses to chip select 5 memory space.

0 EMA_WAIT[0] pin is used to control external wait states.

1h EMA_WAIT[1] pin is used to control external wait states.

2h-3h Reserved

21-20 CS4_WAIT 0-3h Chip Select 4 WAIT signal selection. This signal determines which EMA_WAIT[n] signal will be

used for memory accesses to chip select 4 memory space.

0 EMA_WAIT[0] pin is used to control external wait states.

1h EMA_WAIT[1] pin is used to control external wait states.

2h-3h Reserved

19-18 CS3_WAIT 0-3h Chip Select 3 WAIT signal selection. This signal determines which EMA_WAIT[n] signal will be

used for memory accesses to chip select 3 memory space.

0 EMA_WAIT[0] pin is used to control external wait states.

1h EMA_WAIT[1] pin is used to control external wait states.

2h-3h Reserved

17-16 CS2_WAIT 0-3h Chip Select 2 WAIT signal selection. This signal determines which EMA_WAIT[n] signal will be

used for memory accesses to chip select 2 memory space.

0 EMA_WAIT[0] pin is used to control external wait states..

1h EMA_WAIT[1] pin is used to control external wait states.

2h-3h Reserved

15-8 Reserved 0 Reserved

7-0 MAX_EXT_WAIT 0-FFh Maximum extended wait cycles. The EMIFA will wait for a maximum of (MAX_EXT_WAIT + 1)

× 16 clock cycles before it stops inserting asynchronous wait cycles and proceeds to the hold

period of the access.

Loading...

Loading...