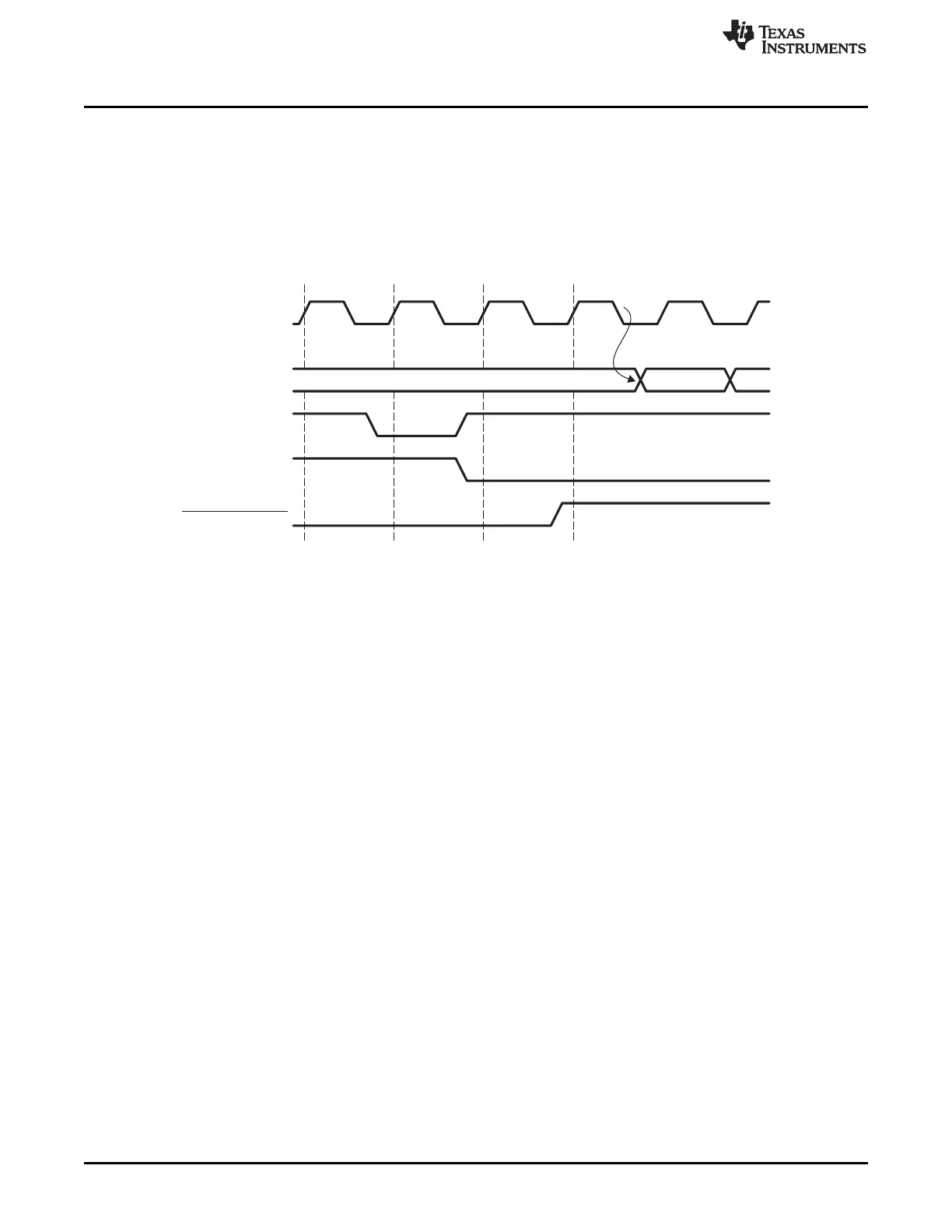

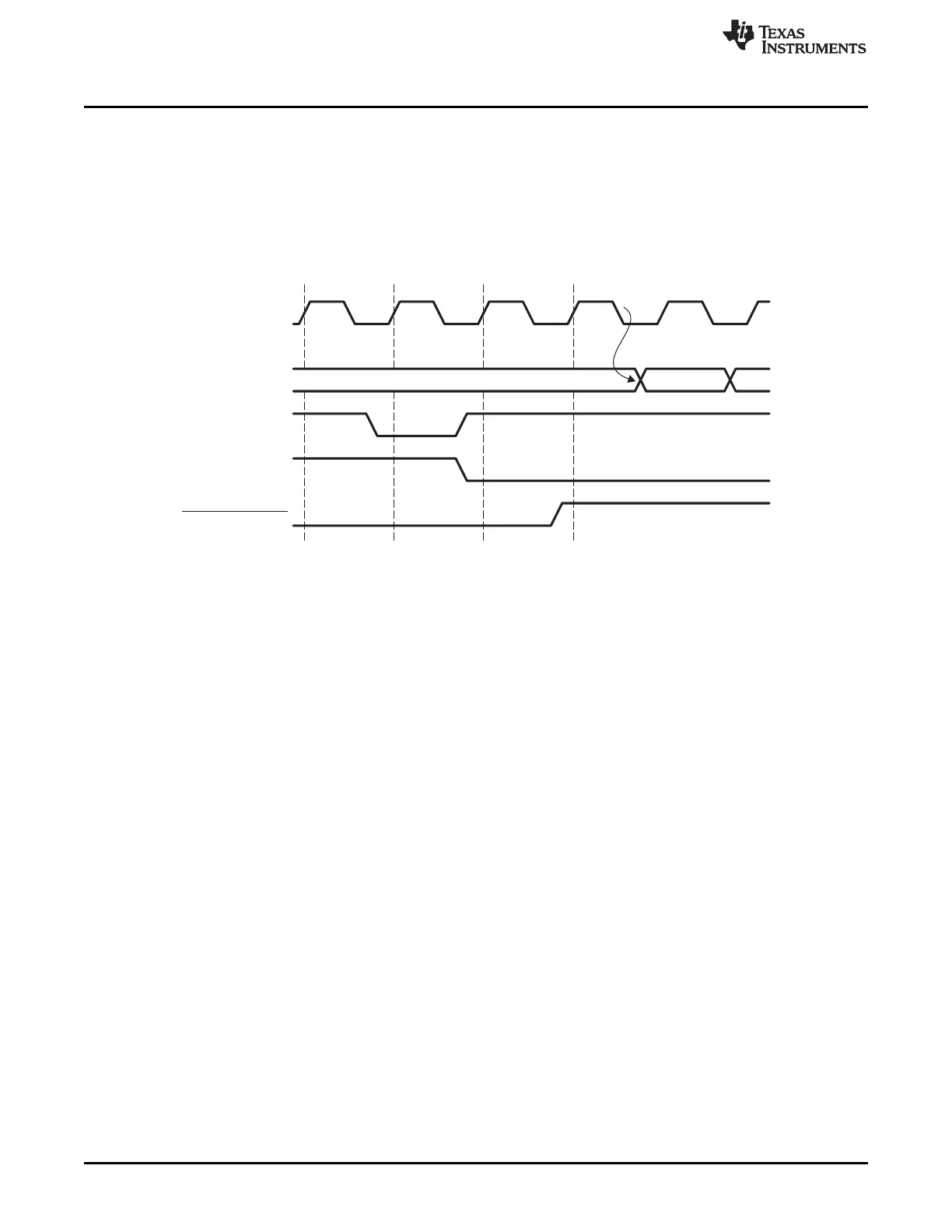

IPC=1

LCD_PCLK

LCD_D[x:0]

LCD_HSYNC

LCD_VSYNC

Pixel0

LCD_AC_ENB_CS

Registers

www.ti.com

976

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Liquid Crystal Display Controller (LCDC)

In Figure 23-37:

• IPC = 1, pixel data is driven on the falling edge of the pixel clock.

• SYNC_CTRL = 1, LCD_HSYNC and LCD_VSYNC signals are driven according to the SYNC_EDGE

bit.

• SYNC_EDGE = 0, LCD_HSYNC and LCD_VSYNC signals are driven on the falling edge of the pixel

clock.

Figure 23-37. SYNC_CTRL = 1, SYNC_EDGE = 0, and IPC = 1

23.3.11.8 Horizontal and Vertical Sync Control (SYNC_CTRL)

This bit enables/disables the possibility to make HSYNC and VSYNC programmable.

• When SYNC_CTRL = 1, HSYNC and VSYNC are driven according to the SYNC_EDGE bit.

• When SYNC_CTRL = 0, HSYNC and VSYNC are driven on opposite edges of the pixel clock from

pixel data.

Loading...

Loading...