Registers

www.ti.com

770

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface A (EMIFA)

18.4.10 EMIFA Interrupt Mask Set Register (INTMSKSET)

The EMIFA interrupt mask set register (INTMSKSET) is used to enable the Asynchronous Timeout

Interrupt. If read as 1, the AT_MASKED bit in the EMIFA interrupt masked register (INTMSK) will be set

and an interrupt will be generated when an Asynchronous Timeout occurs. If read as 0, the AT_MASKED

bit will always read 0 and no interrupt will be generated when an Asynchronous Timeout occurs. Writing a

1 to the AT_MASK_SET bit enables the Asynchronous Timeout Interrupt. The EMIFA on some devices

does not have the EMA_WAIT pin; therefore, these registers and fields are reserved on those devices.

The INTMSKSET is shown in Figure 18-40 and described in Table 18-58.

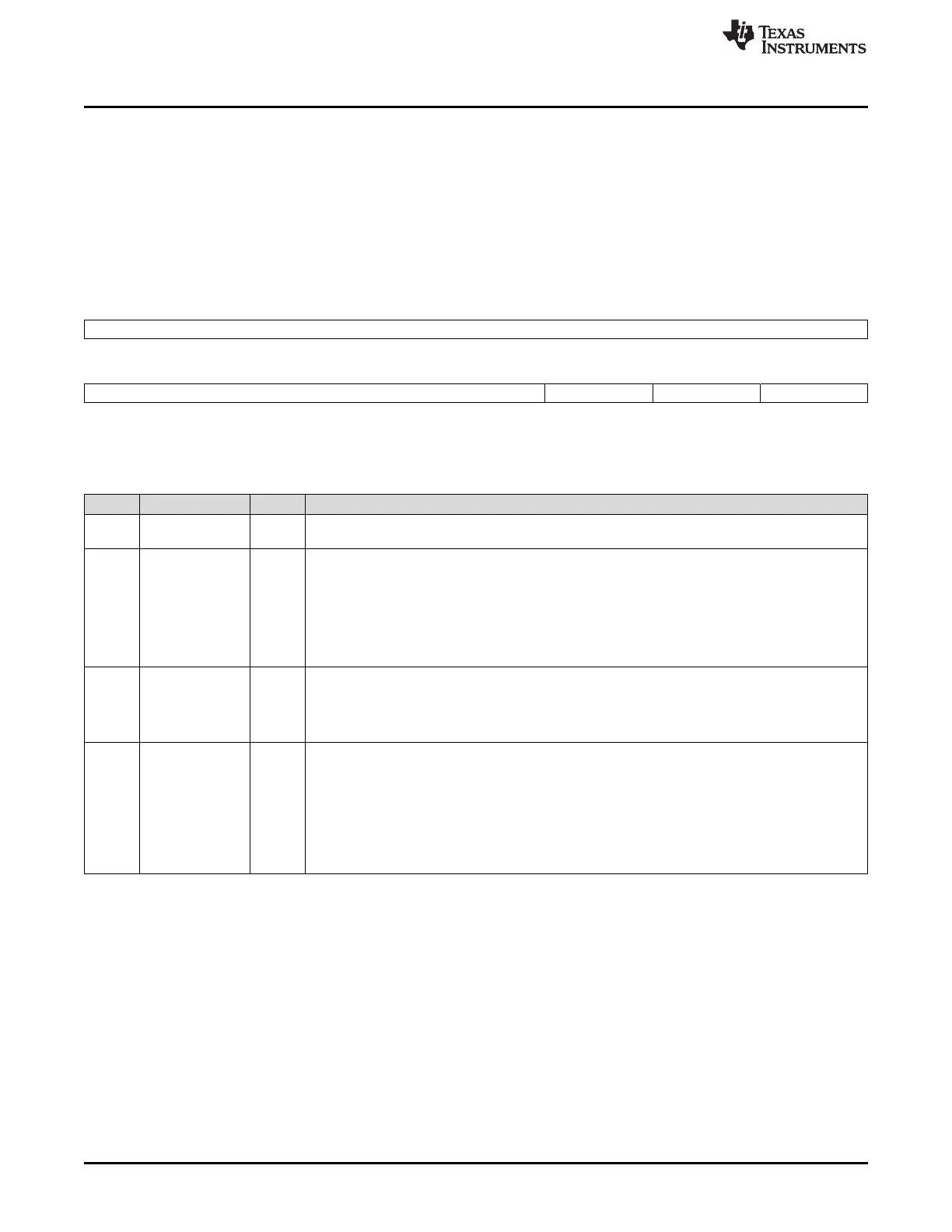

Figure 18-40. EMIFA Interrupt Mask Set Register (INTMSKSET)

31 16

Reserved

R-0

15 3 2 1 0

Reserved WR_MASK_SET Reserved AT_MASK_SET

R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

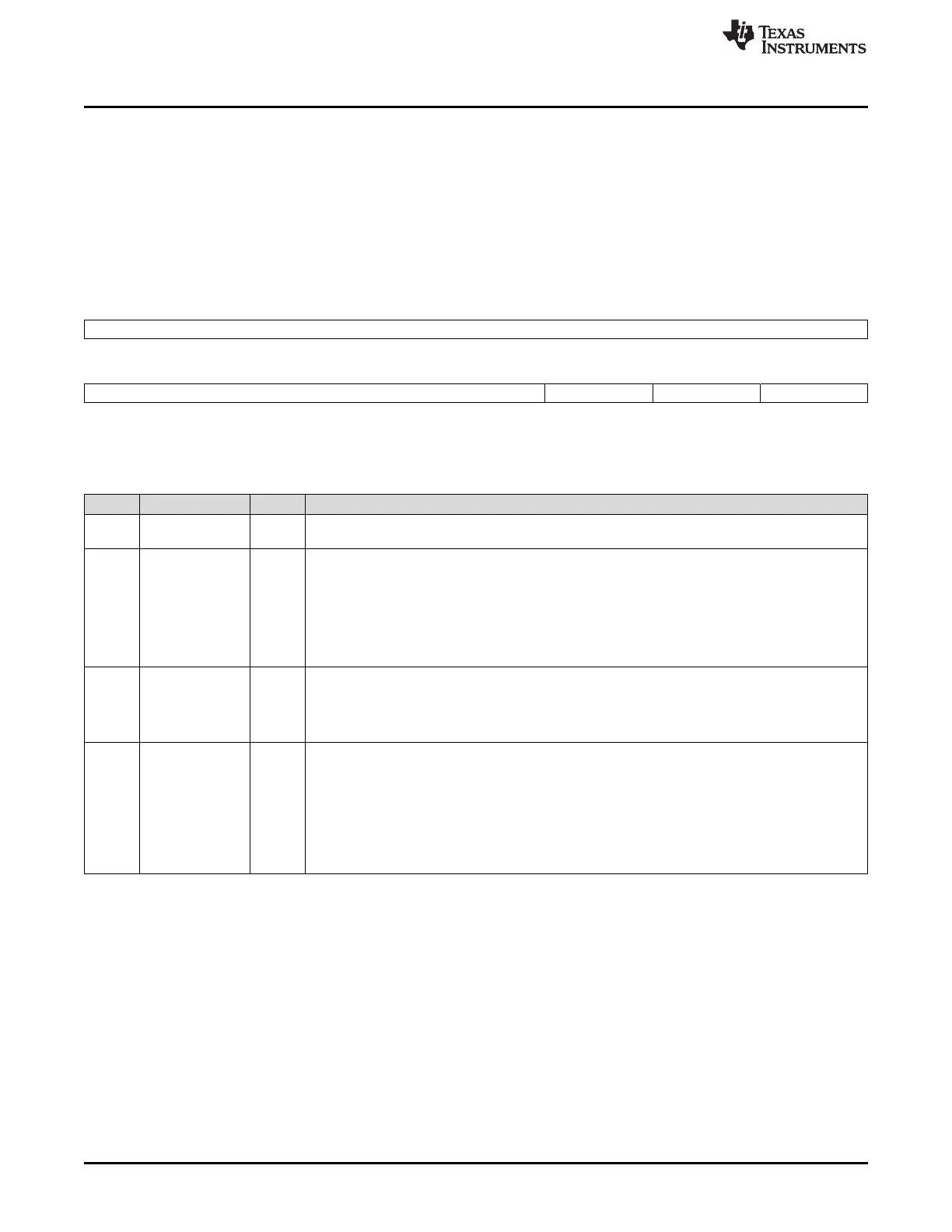

Table 18-58. EMIFA Interrupt Mask Set Register (INTMSKSET) Field Descriptions

Bit Field Value Description

31-3 Reserved 0 Reserved. The reserved bit location is always read as 0. If writing to this field, always write the

default value of 0.

2 WR_MASK_SET Wait Rise Mask Set. This bit determines whether or not the wait rise Interrupt is enabled. Writing a

1 to this bit sets this bit, sets the WR_MASK_CLR bit in the EMIFA interrupt mask clear register

(INTMSKCLR), and enables the wait rise interrupt. To clear this bit, a 1 must be written to the

WR_MASK_CLR bit in INTMSKCLR.

0 Indicates that the wait rise interrupt is disabled. Writing a 0 has no effect.

1 Indicates that the wait rise interrupt is enabled. Writing a 1 sets this bit and the WR_MASK_CLR bit

in the EMIFA interrupt mask clear register (INTMSKCLR).

1 LT_MASK_SET Mask set for LT_MASKED bit in the EMIFA interrupt mask register (INTMSK).

0 Indicates that the line trap interrupt is disabled. Writing a 0 has no effect.

1 Indicates that the line trap interrupt is enabled. Writing a 1 sets this bit and the LT_MASK_CLR bit

in the EMIFA interrupt mask clear register (INTMSKCLR).

0 AT_MASK_SET Asynchronous Timeout Mask Set. This bit determines whether or not the Asynchronous Timeout

Interrupt is enabled. Writing a 1 to this bit sets this bit, sets the AT_MASK_CLR bit in the EMIFA

interrupt mask clear register (INTMSKCLR), and enables the Asynchronous Timeout Interrupt. To

clear this bit, a 1 must be written to the AT_MASK_CLR bit of the EMIFA interrupt mask clear

register (INTMSKCLR).

0 Indicates that the Asynchronous Timeout Interrupt is disabled. Writing a 0 has no effect.

1 Indicates that the Asynchronous Timeout Interrupt is enabled. Writing a 1 sets this bit and the

AT_MASK_CLR bit in the EMIFA interrupt mask clear register (INTMSKCLR).

Loading...

Loading...