Write FIFO

control logic

Host write

pointer

HPI DMA

read pointer

Write FIFO

Host

writes

Read FIFO

reads

Host

control logic

Read FIFO

Host read

pointer

HPI DMA

write pointer

HPI

DMA

logic

Processor

memory

Burst

writes

reads

Burst

Architecture

www.ti.com

874

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Host Port Interface (HPI)

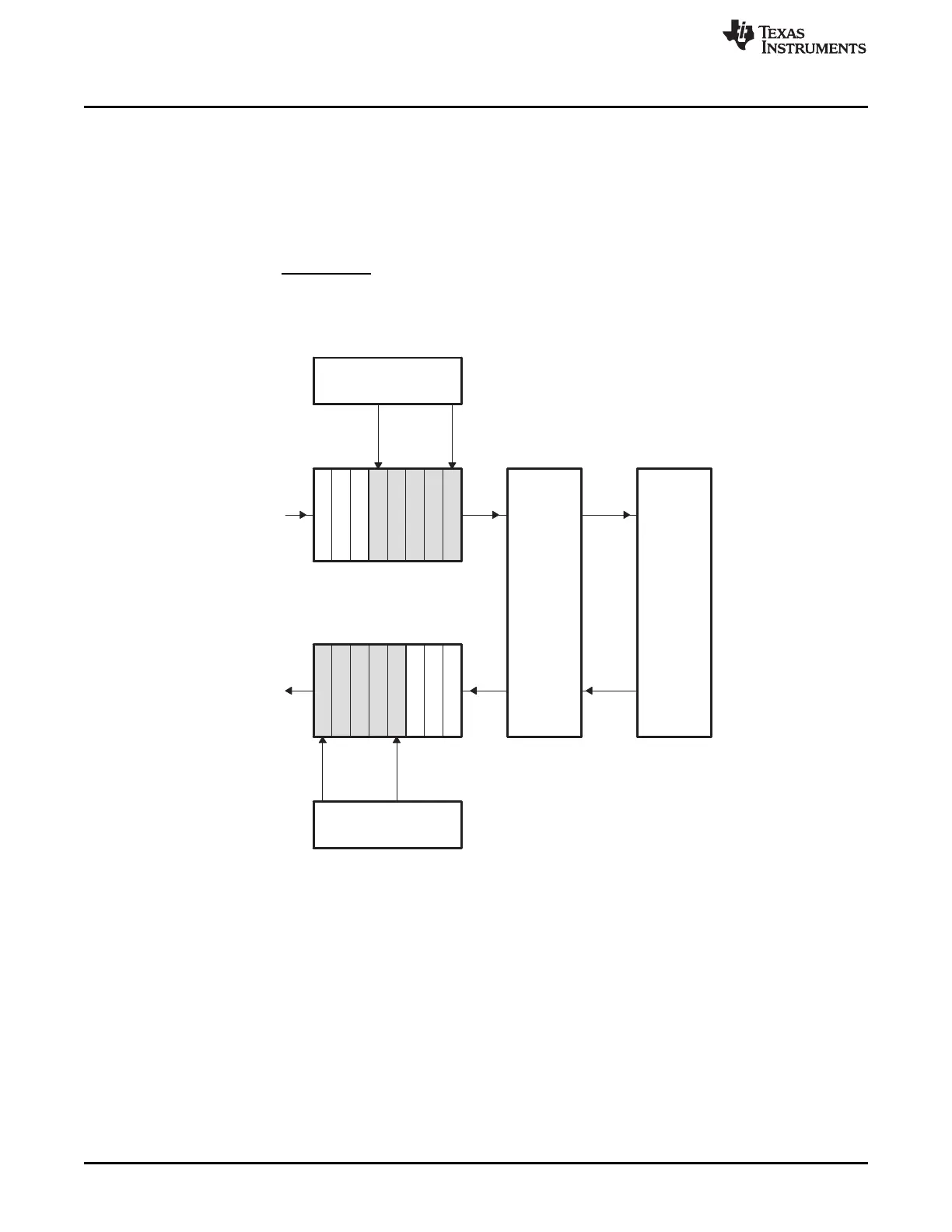

21.2.6.10 FIFOs and Bursting

The HPI data register (HPID) is a port through which the host accesses two first-in, first-out buffers

(FIFOs). As shown in Figure 21-14, a read FIFO supports host read cycles, and a write FIFO supports

host write cycles. Both read and write FIFOs are 8-words deep (each word is 32 bits). If the host is

performing multiple reads or writes to consecutive memory addresses (autoincrement HPID cycles), the

FIFOs are used for bursting. The HPI DMA logic reads or writes a burst of four words at a time when

accessing one of the FIFOs.

Bursting is essentially invisible to the host because the host interface signaling is not affected. Its benefit

to the host is that the UHPI_HRDY signal is deasserted less often when there are multiple reads or writes

to consecutive addresses.

Figure 21-14. FIFOs in the HPI

Loading...

Loading...