www.ti.com

Registers

925

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Inter-Integrated Circuit (I2C) Module

22.3.16 I2C Pin Function Register (ICPFUNC)

The I2C pin function register (ICPFUNC) is used to configure the external I2C pins (I2Cx_SDA and

I2Cx_SCL) as a I2C peripheral pin or a GPIO pin. ICPFUNC is shown in Figure 22-30 and described in

Table 22-23.

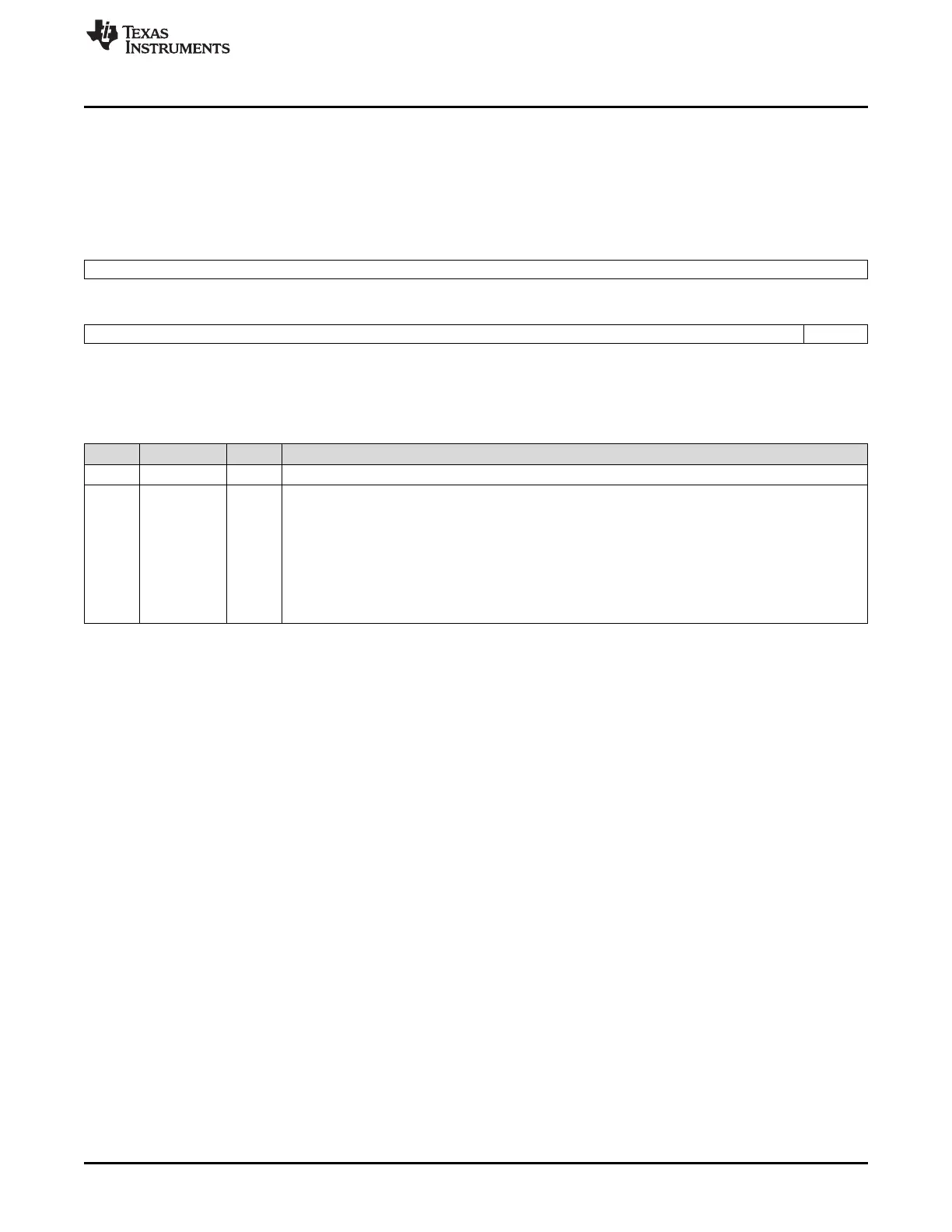

Figure 22-30. I2C Pin Function Register (ICPFUNC)

31 16

Reserved

R-0

15 1 0

Reserved PFUNC0

R-0 R/W-0

LEGEND: R/W = Read/Write; R= Read only; -n = value after reset

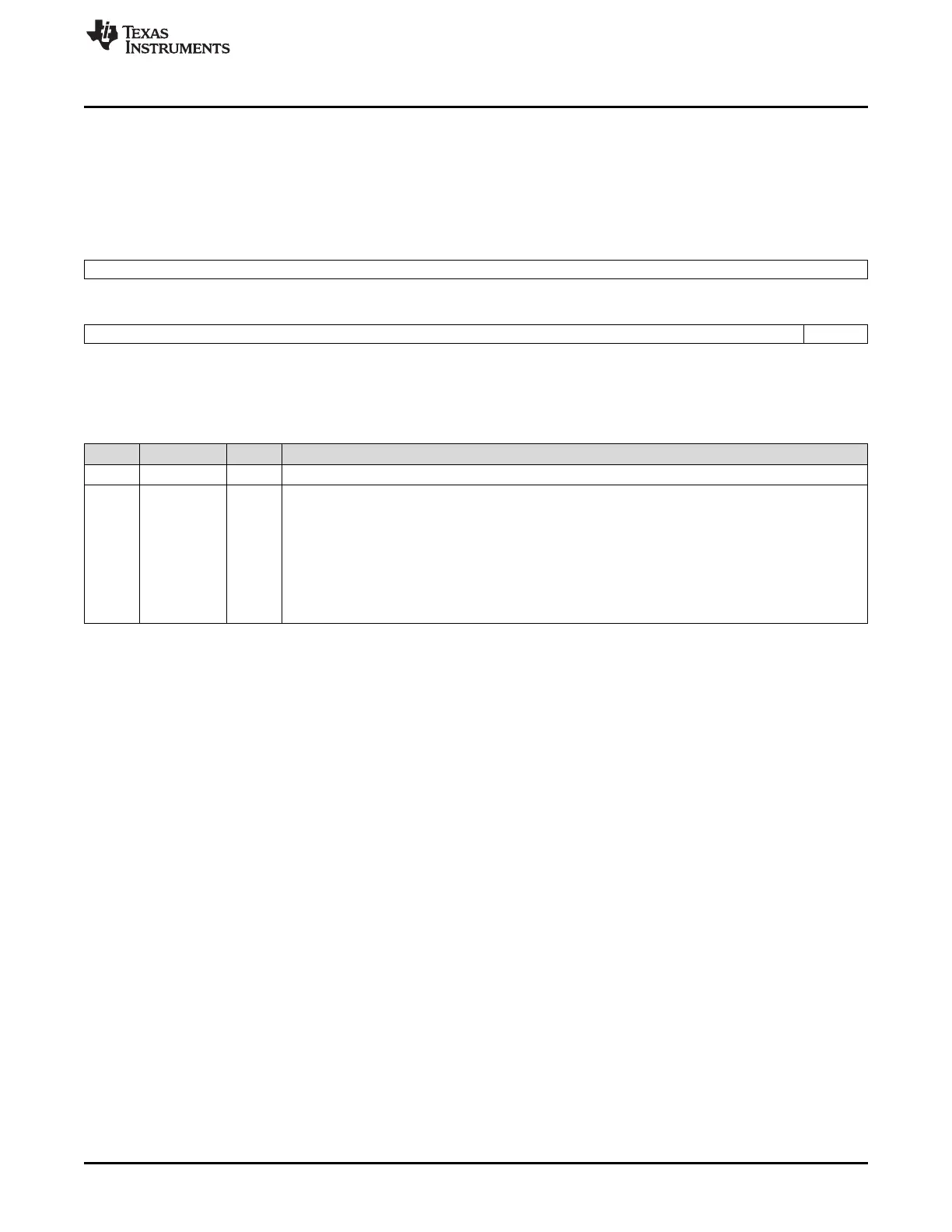

Table 22-23. I2C Pin Function Register (ICPFUNC) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 These reserved bit locations are always read as zeros. A value written to this field has no effect.

0 PFUNC0 Controls the function of the I2Cx_SCL and I2Cx_SDA pins.

0 Pins function as I2Cx_SCL and I2Cx_SDA.

1 Pins function as GPIO.

Note: No hardware protection is required to disable the I2C function when the PFUNC0 bit and the IRS

bit in the I2C mode register (ICMDR) are both set to 1. When PFUNC0 = 1 (GPIO mode), the sub-

module that controls the I2C function receives the value 1 for I2Cx_SCL and I2Cx_SDA. The IRS bit

can be set to 1 regardless of PFUNC0, and the I2C function works whenever the IRS bit is 1. You are

expected to hold I2C in reset via the IRS bit when changing to/from GPIO mode via the PFUNC0 bit.

Loading...

Loading...