Registers

www.ti.com

772

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface A (EMIFA)

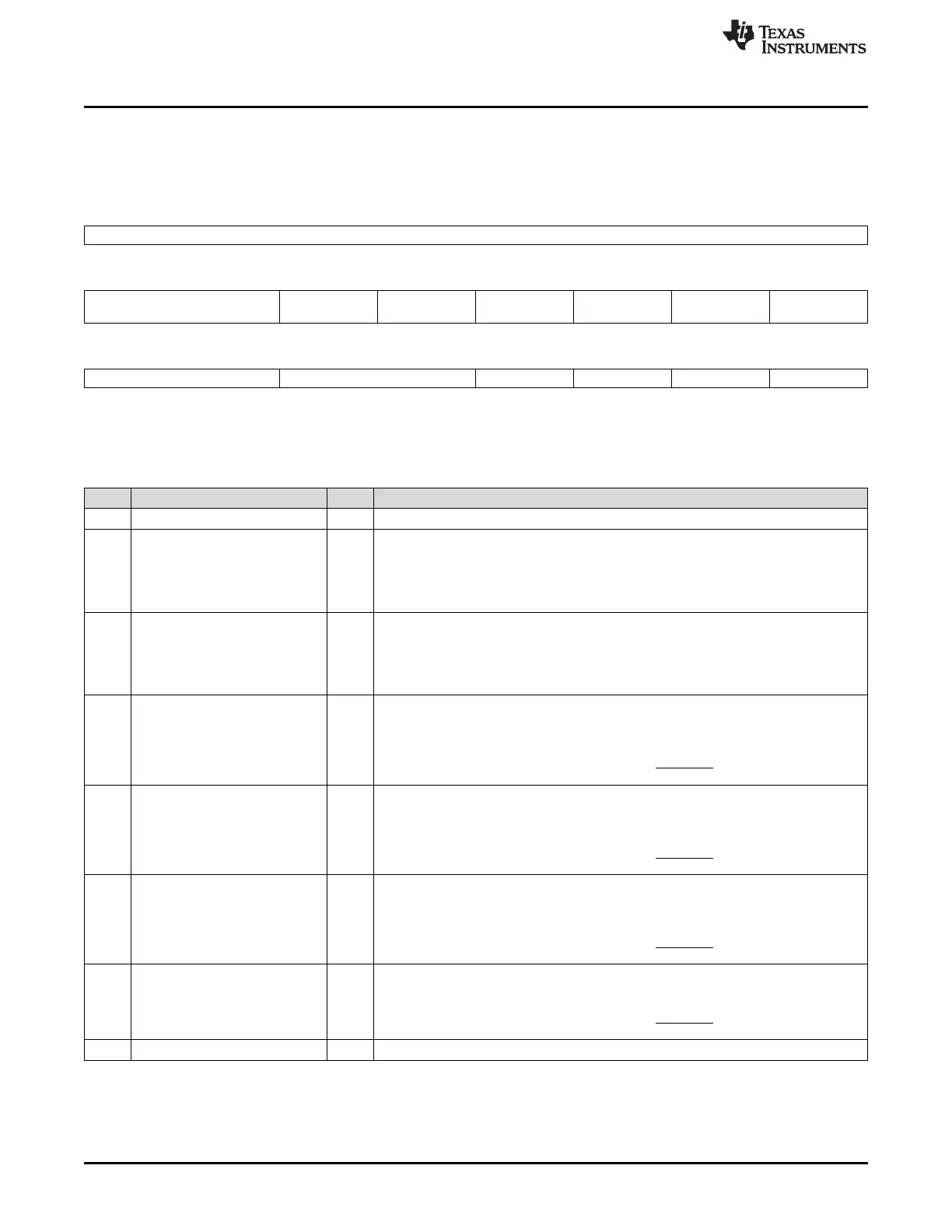

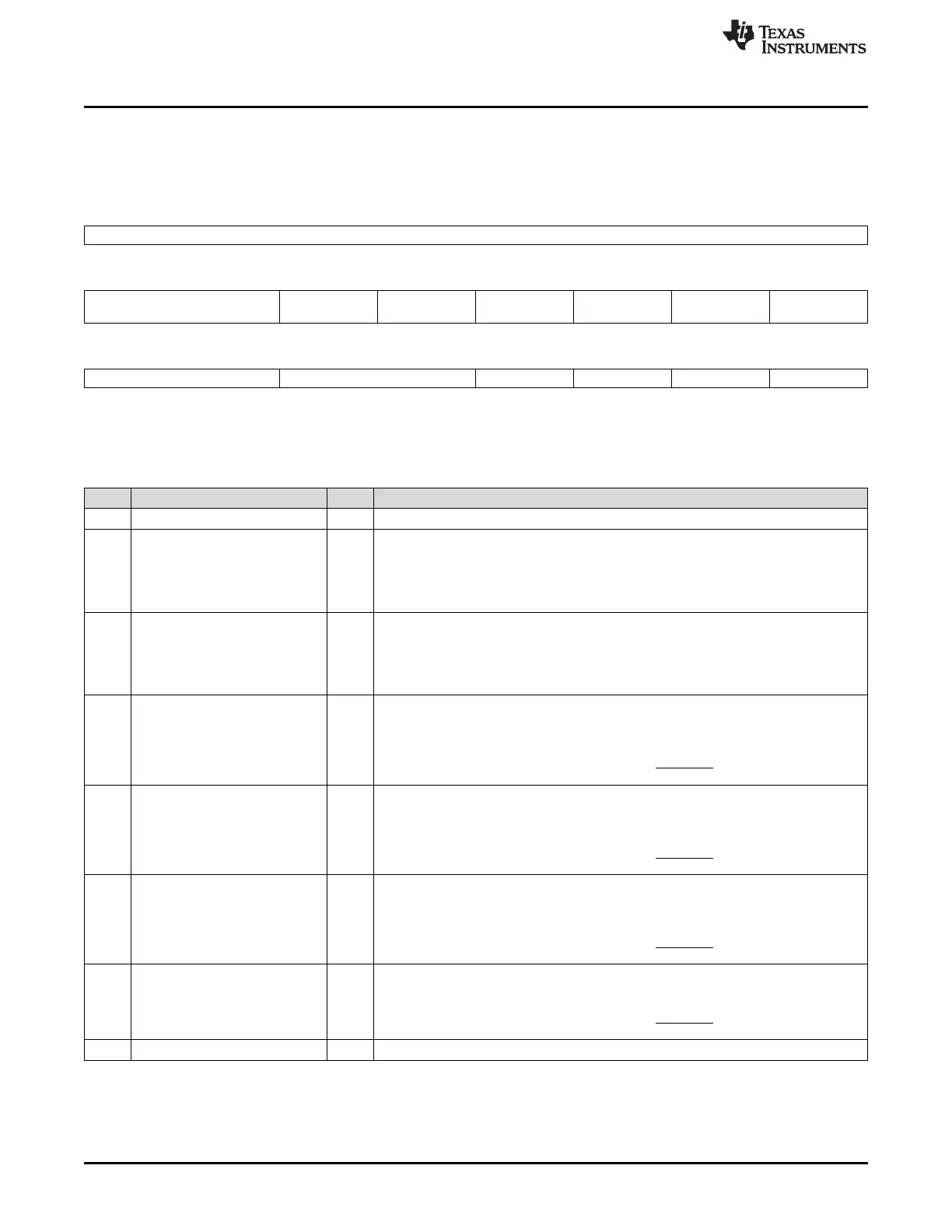

18.4.12 NAND Flash Control Register (NANDFCR)

The NAND Flash control register (NANDFCR) is shown in Figure 18-42 and described in Table 18-60.

Figure 18-42. NAND Flash Control Register (NANDFCR)

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

Reserved 4BITECC_ADD

_CALC_START

4BITECC

_START

CS5ECC CS4ECC CS3ECC CS2ECC

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

Reserved 4BITECCSEL CS5NAND CS4NAND CS3NAND CS2NAND

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 18-60. NAND Flash Control Register (NANDFCR) Field Descriptions

Bit Field Value Description

31-14 Reserved 0 Reserved

13 4BITECC_ADD_CALC_START NAND Flash 4-bit ECC address and error value calculation Start. Set to 1 to start 4_bit

ECC error address and error value calculation on read syndrome. This bit is cleared

when any of the NAND Flash error address registers or NAND Flash error value

registers are read.

1 start 4_bit ECC error address and error value calculation on read syndrome.

12 4BITECC_START Nand Flash 4-bit ECC start for the selected chip select. Set to 1 to start 4_bit ECC

calculation on data for NAND Flash on chip select selected by bit 4BITECCSEL. This

bit is cleared when ay of the NAND Flash 4_bit ECC registers are read.

1 start 4_bit ECC calculation on data for NAND Flash on chip select selected by bit

4BITECCSEL.

11 CS5ECC NAND Flash ECC start for chip select 5. Set to 1 to start 1_bit ECC calculation on data

for NAND Flash for this chip select. This bit is cleared when CS5 1_bit ECC register is

read.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EMA_CS5.

10 CS4ECC NAND Flash ECC start for chip select 4. Set to 1 to start 1_bit ECC calculation on data

for NAND Flash for this chip select. This bit is cleared when CS4 1_bit ECC register is

read.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EMA_CS4.

9 CS3ECC NAND Flash ECC start for chip select 3. Set to 1 to start 1_bit ECC calculation on data

for NAND Flash for this chip select. This bit is cleared when CS3 1_bit ECC register is

read.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EMA_CS3.

8 CS2ECC NAND Flash ECC start for chip select 2. This bit is cleared when CS2 1_bit ECC

register is read.

0 Do not start ECC calculation.

1 Start ECC calculation on data for NAND Flash on EMA_CS2.

7-6 Reserved 0 Reserved

Loading...

Loading...