Registers

www.ti.com

564

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

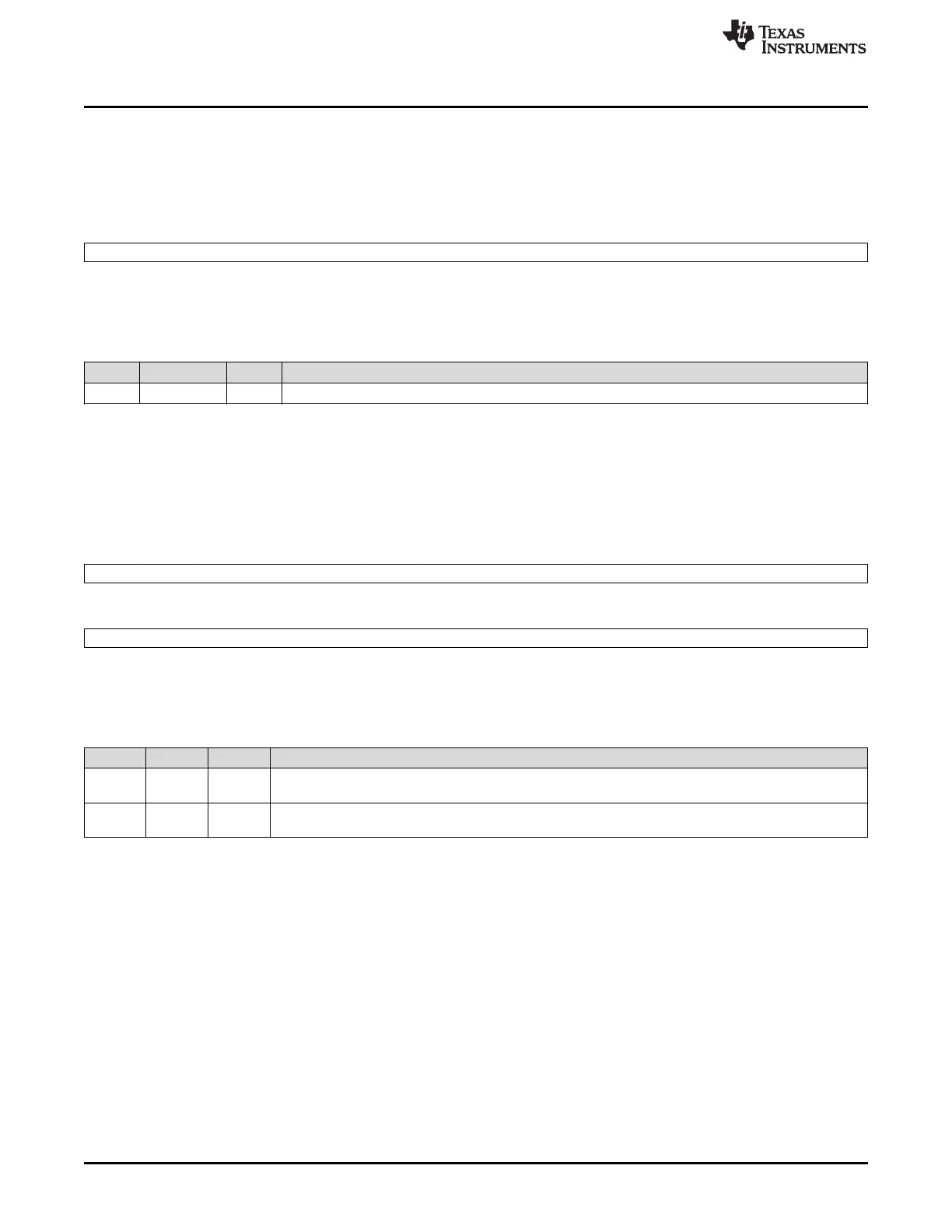

16.4.3.6.14 Destination FIFO Source Address Register n (DFSRCn)

The destination FIFO source address register n (DFSRCn) is shown in Figure 16-104 and described in

Table 16-84.

Figure 16-104. Destination FIFO Source Address Register n (DFSRCn)

31 0

SADDR

R-0

LEGEND: R = Read only; -n = value after reset

Table 16-84. Destination FIFO Source Address Register n (DFSRCn) Field Descriptions

Bit Field Value Description

31-0 SADDR 0 Always Read as 0.

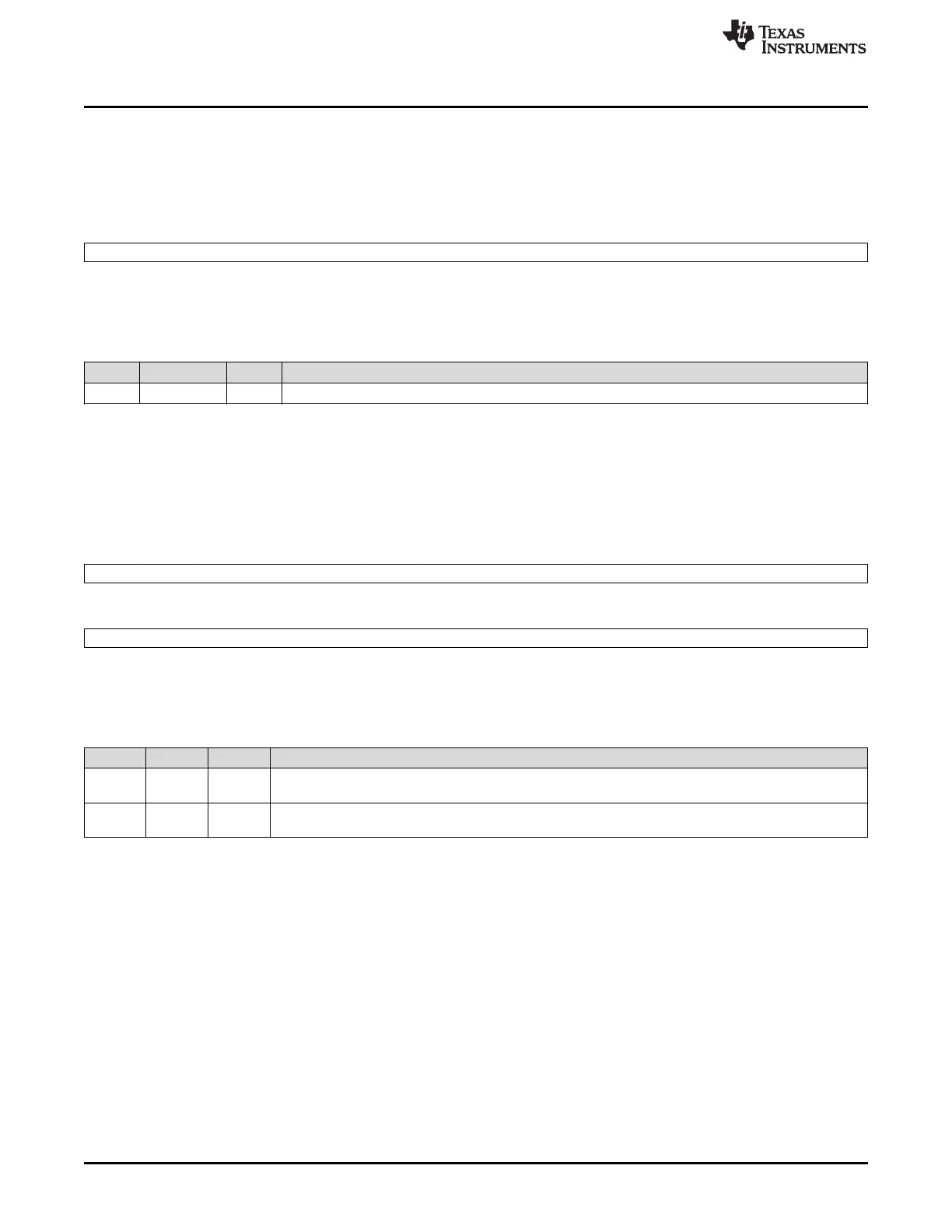

16.4.3.6.15 Destination FIFO Count Register n (DFCNTn)

The destination FIFO count register n (DFCNTn) is shown in Figure 16-105 and described in Table 16-85.

Figure 16-105. Destination FIFO Count Register n (DFCNTn)

31 16

BCNT

R-0

15 0

ACNT

R-0

LEGEND: R = Read only; -n = value after reset

Table 16-85. Destination FIFO Count Register n (DFCNTn) Field Descriptions

Bit Field Value Description

31-16 BCNT 0-FFFFh B-dimension count. Number of arrays to be transferred, where each array is ACNT in length. Count/count

remaining for destination register set. Represents the amount of data remaining to be written.

15-0 ACNT 0-FFFFh A-dimension count. Number of bytes to be transferred in first dimension count/count remaining for

destination register set. Represents the amount of data remaining to be written.

Loading...

Loading...