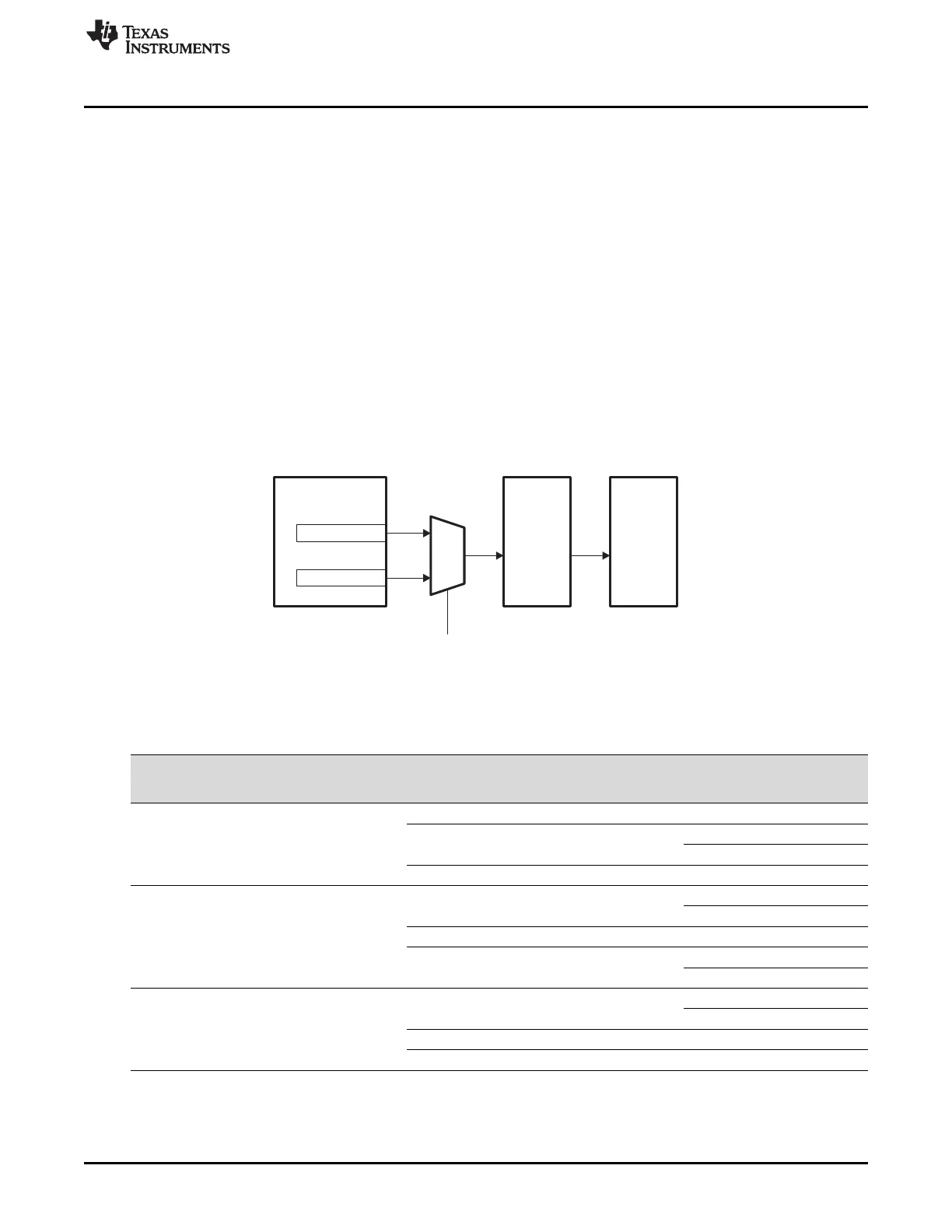

SYSCLK3

DIV4P5CLK

PLL Controller

0

1

CFGCHIP3[EMA_CLKSRC]

LPSC

EMIFA

www.ti.com

Peripheral Clocking

111

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Device Clocking

6.3.3 EMIFA Clocking

EMIFA requires a single input clock source. The EMIFA clock can be sourced from either SYSCLK3 or

DIV4P5 (see Figure 6-4). The EMA_CLKSRC bit in the chip configuration 3 register (CFGCHIP3) of the

System Configuration Module controls whether SYSCLK3 or DIV4P5 is selected as the clock source for

EMIFA.

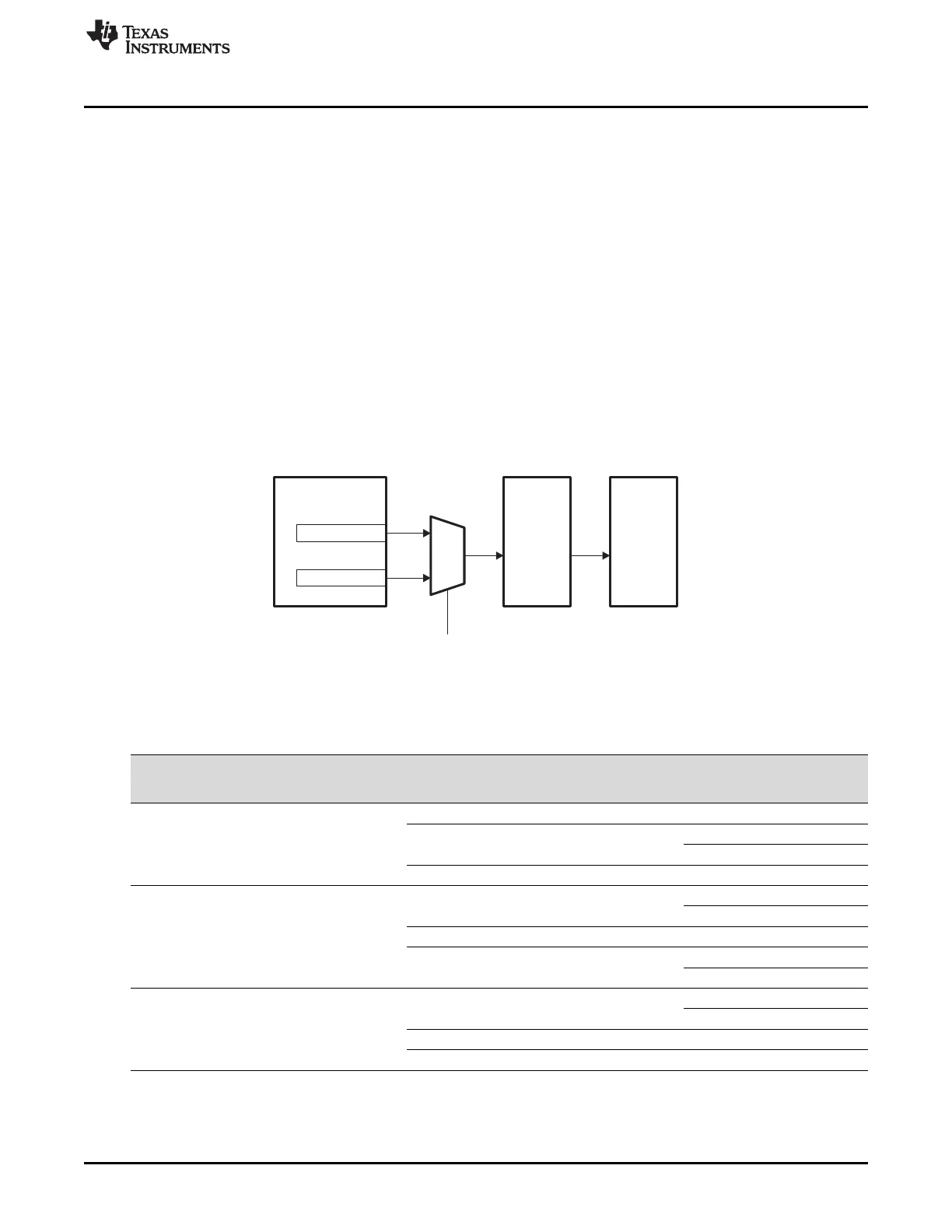

Selecting the appropriate clock source for EMIFA is determined by the desired clock rate. Table 6-6 shows

example PLL register settings and the resulting DIV4P5 and SYSCLK3 frequencies based on the OSCIN

reference clock frequency of 25 MHz. From these example configurations, the following observations can

be made:

• To achieve a typical frequency of 100 MHz supported by EMIFA and the typical CPU frequency of 300

MHz, the output of the PLL multiplier should be set to 600 MHz and the EMA_CLK source should be

set to SYSCLK3 with the PLLDIV3 register set to 3.

• The frequency of the DIV4P5 clock is fixed at the output frequency of the PLL multiplier block divided

by 4.5.

• The PLLDIV3 block that sets the divider ratio for SYSCLK3 can be changed to achieve various clock

frequencies.

Figure 6-4. EMIFA Clocking Diagram

(1)

See Section 6.2 for explanation of POSTDIV divider modes.

Table 6-6. EMIFA Frequencies

OSCIN

Frequency

PLL Multiplier

Register

Setting

Multiplier

Frequency

(MHz)

Post Divider

Mode

(1)

POSTDIV

Output

Frequency DIV4P5

PLLDIV3

Register

Setting SYSCLK3

25 24 600 Div2 300 MHz 133 MHz 2 100 MHz

Div3 200 MHz 133 MHz 2 66.6 MHz

1 100 MHz

Div4 150 MHz 133 MHz 1 75 MHz

25 18 450 Div2 225 MHz 100 MHz 3 56.3 MHz

2 75 MHz

Div3 150 MHz 100 MHz 1 75 MHz

Div4 112.5 MHz 100 MHz 1 56.3 MHz

0 112.5 MHz

25 16 400 Div2 200 MHz 89 MHz 2 66.6 MHz

1 100 MHz

Div3 133 MHz 89 MHz 1 66.5 MHz

Div4 100 MHz 89 MHz 0 100 MHz

Loading...

Loading...