SYSCFG Registers

www.ti.com

182

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

System Configuration (SYSCFG) Module

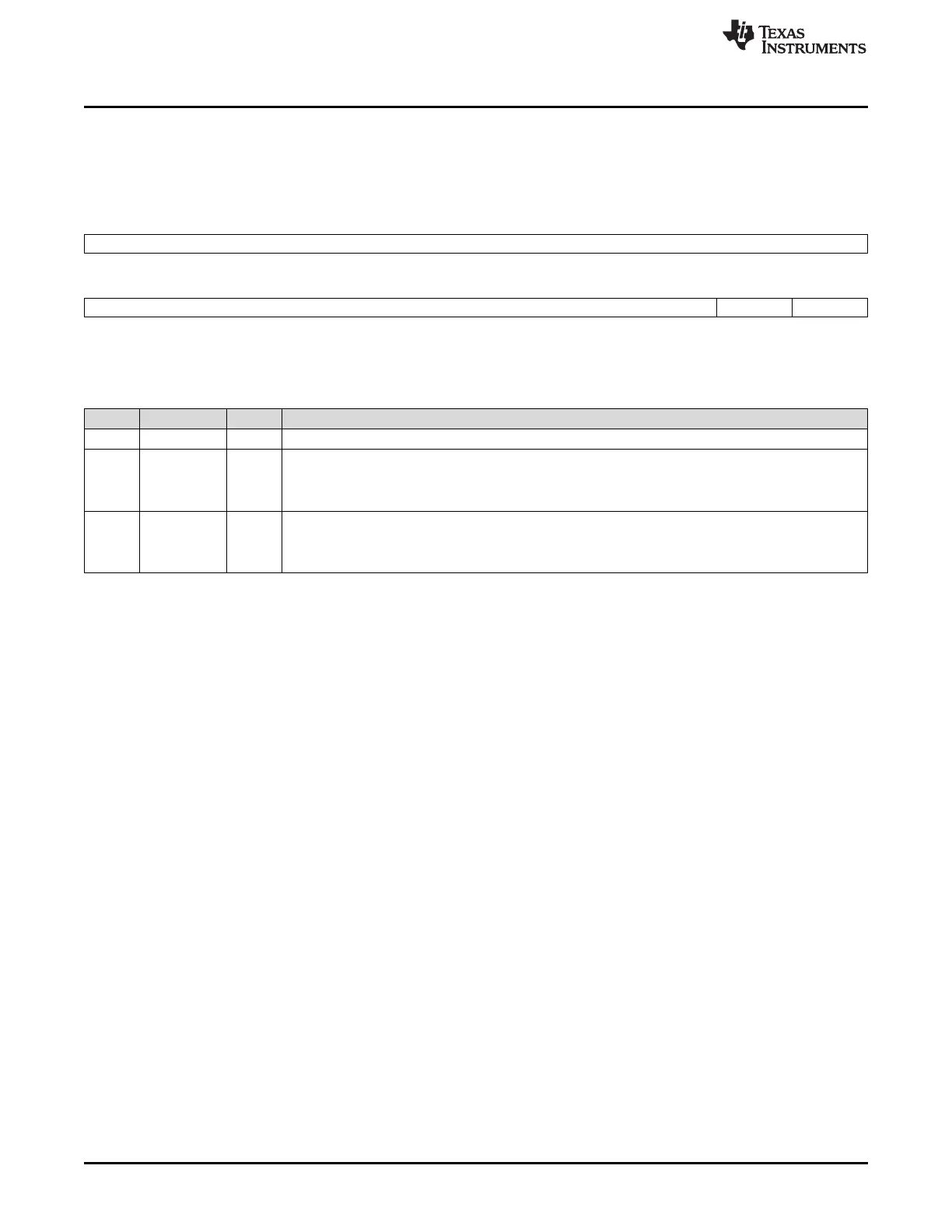

10.5.7.2 Interrupt Enable Status/Clear Register (IENSTAT)

The interrupt enable status/clear register (IENSTAT) shows the status of enabled interrupt and allows

clearing of the interrupt status. The IENSTAT is shown in Figure 10-9 and described in Table 10-13.

Figure 10-9. Interrupt Enable Status/Clear Register (IENSTAT)

31 16

Reserved

R-0

15 2 1 0

Reserved ADDRERR PROTERR

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

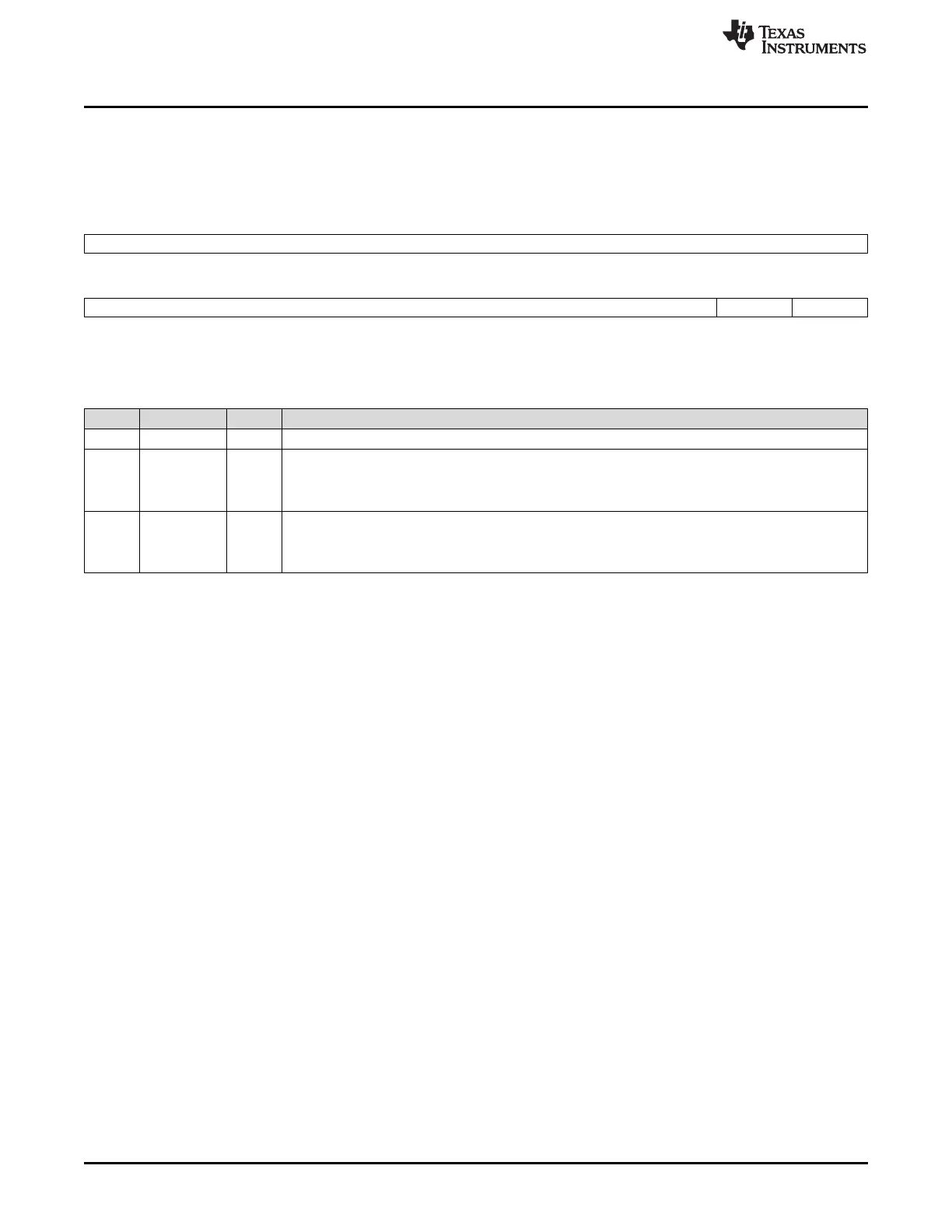

Table 10-13. Interrupt Enable Status/Clear Register (IENSTAT) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved. Always read 0.

1 ADDRERR Addressing violation error. Reading this bit field reflects the interrupt enabled status.

0 Indicates the interrupt is not set. Writing 0 has no effect.

1 Indicates the interrupt is set. Writing 1 clears the status.

0 PROTERR Protection violation error. Reading this bit field reflects the interrupt enabled status.

0 Indicates the interrupt is not set. Writing 0 has no effect.

1 Indicates the interrupt is set. Writing 1 clears the status.

Loading...

Loading...