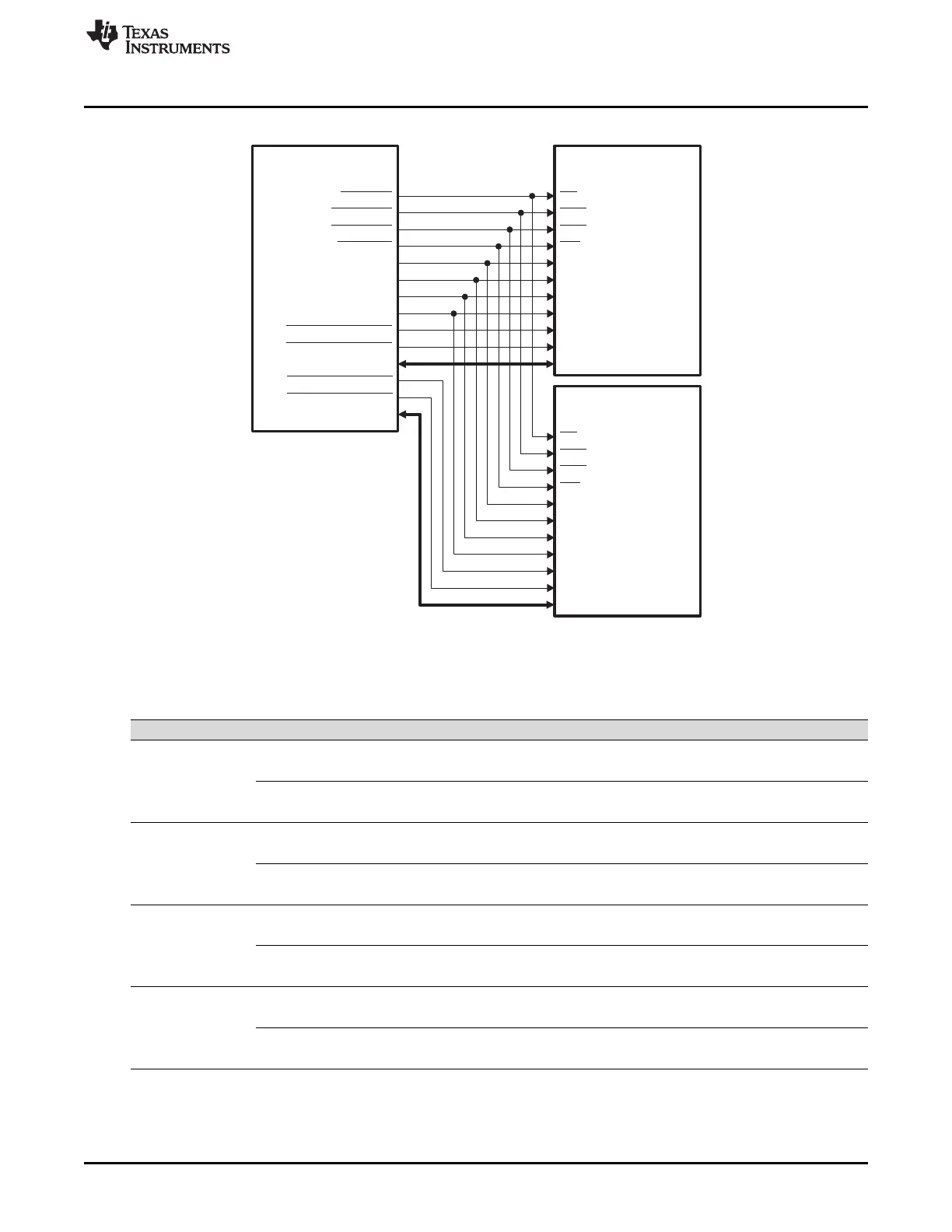

EMB_CS

EMB_CAS

EMB_RAS

EMB_WE

EMB_CLK

EMB_SDCKE

EMB_BA[1:0]

EMB_A[12:0]

EMB_WE_DQM[0]

EMB_D[15:0]

EMIFB

CE

CAS

RAS

WE

CLK

CKE

BA[1:0]

A[12:0]

LDQM

DQ[15:0]

SDRAM

4Mx16x4

Bank

EMB_WE_DQM[1]

UDQM

EMB_WE_DQM[2]

EMB_D[31:16]

EMB_WE_DQM[3]

CE

CAS

RAS

WE

CLK

CKE

BA[1:0]

A[12:0]

LDQM

DQ[15:0]

SDRAM

4Mx16x4

Bank

UDQM

www.ti.com

Architecture

787

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

External Memory Interface B (EMIFB)

Figure 19-5. EMIFB to Dual 4M × 16 × 4 bank SDRAM Interface

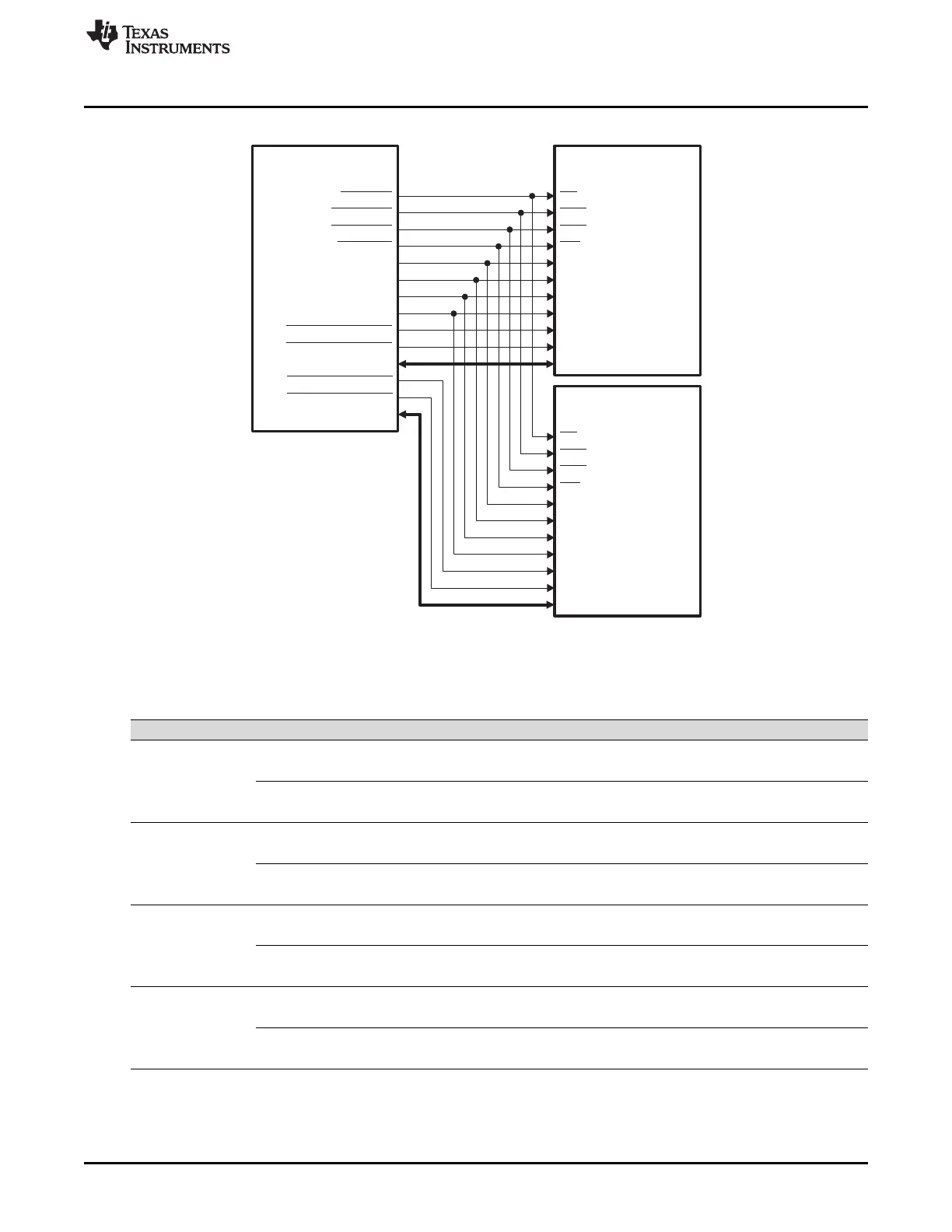

Table 19-4. Example of 32-bit EMIFB Address Pin Connections

SDRAM Size Width Banks Address Pins

64M bits ×16 4 SDRAM A[11:0]

EMIFB EMB_A[11:0]

×32 4 SDRAM A[10:0]

EMIFB EMB_A[10:0]

128M bits ×16 4 SDRAM A[11:0]

EMIFB EMB_A[11:0]

×32 4 SDRAM A[11:0]

EMIFB EMB_A[11:0]

256M bits ×16 4 SDRAM A[12:0]

EMIFB EMB_A[12:0]

×32 4 SDRAM A[11:0]

EMIFB EMB_A[11:0]

512M bits ×16 4 SDRAM A[12:0]

EMIFB EMB_A[12:0]

×32 4 SDRAM A[12:0]

EMIFB EMB_A[12:0]

Loading...

Loading...