www.ti.com

PSC Registers

157

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Power and Sleep Controller (PSC)

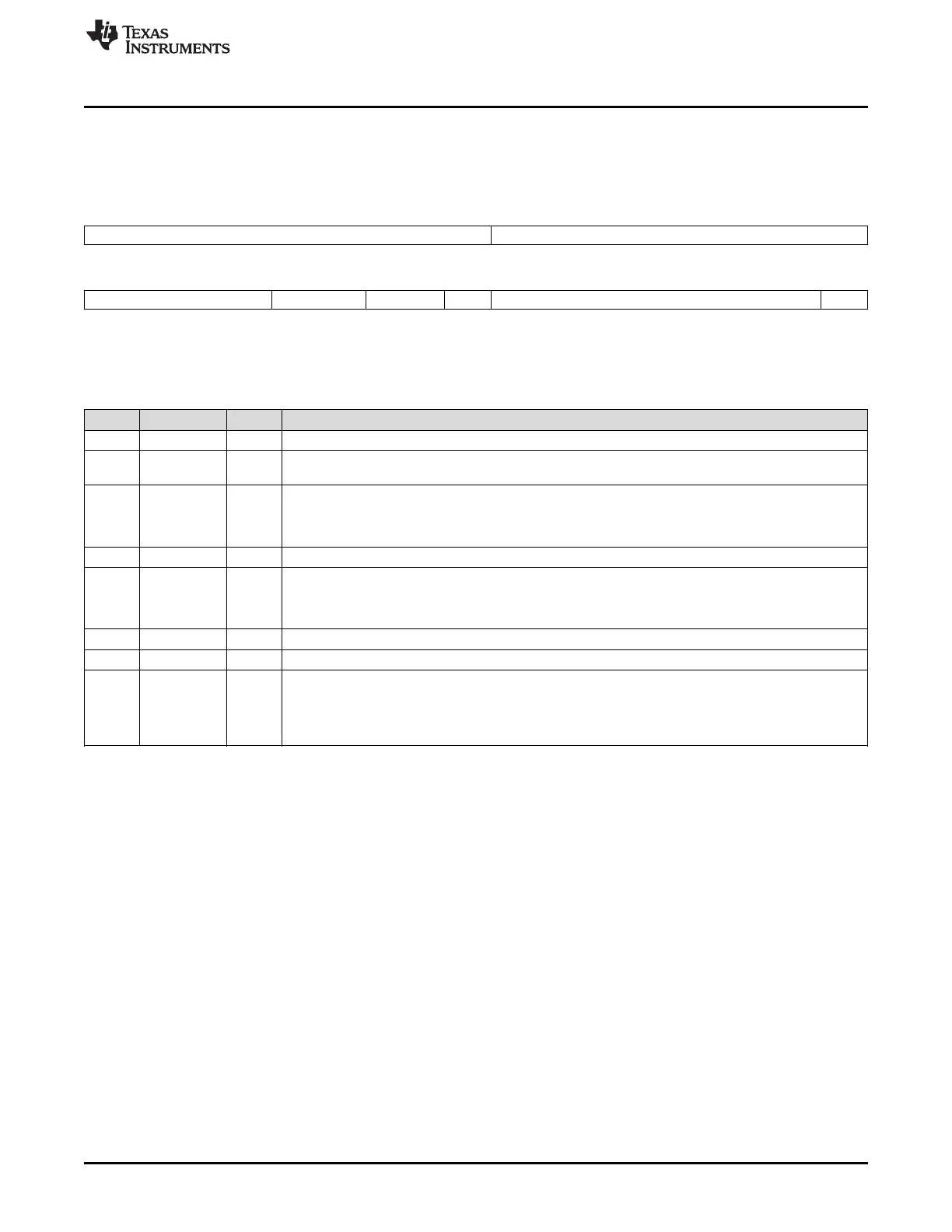

8.6.13 Power Domain 0 Control Register (PDCTL0)

The power domain 0 control register (PDCTL0) is shown in Figure 8-13 and described in Table 8-18.

Figure 8-13. Power Domain 0 Control Register (PDCTL0)

31 24 23 16

Reserved WAKECNT

R-0 R/W-1Fh

15 12 11 10 9 8 7 1 0

PDMODE Reserved EMUIHBIE Rsvd Reserved NEXT

R-Fh R-0 R/W-0 R-1 R-0 R/W-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

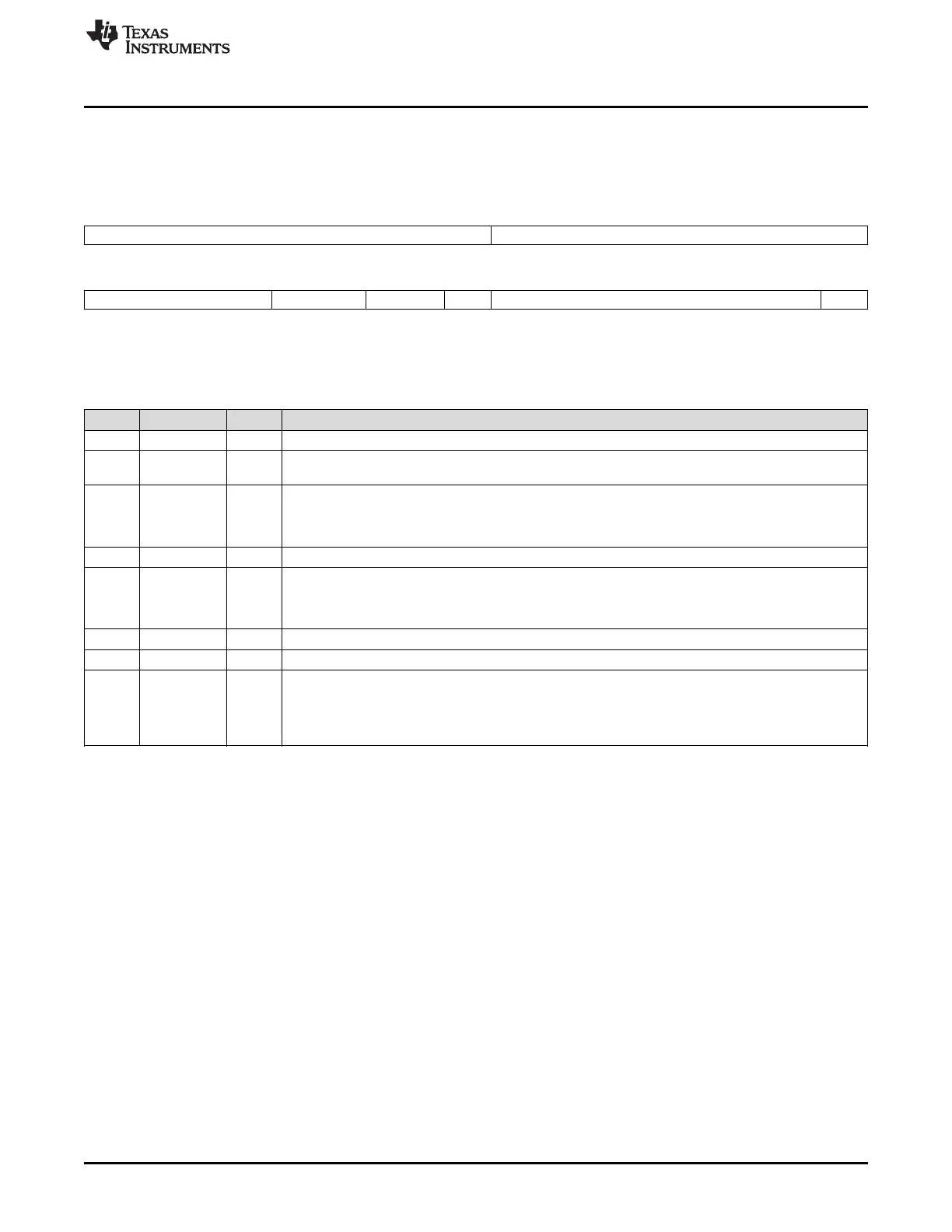

Table 8-18. Power Domain 0 Control Register (PDCTL0) Field Descriptions

Bit Field Value Description

31-24 Reserved 0 Reserved

23-16 WAKECNT 0-FFh RAM wake count delay value. Not recommended to change the default value (1Fh). Bits 23-30:

GOOD2ACCESS wake delay. Bits 19-16: ON2GOOD wake delay.

15-12 PDMODE 0-Fh Power down mode.

0-Eh Reserved

Fh Core on, RAM array on, RAM periphery on.

11-10 Reserved 0 Reserved

9 EMUIHBIE Emulation alters power domain state interrupt enable.

0 Disable interrupt.

1 Enable interrupt.

8 Reserved 1 Reserved

7-1 Reserved 0 Reserved

0 NEXT Power domain next state. For Always ON power domain this bit is read/write, but writes have no effect

since internally this power domain always remains in the on state.

0 Power domain off.

1 Power domain on.

Loading...

Loading...