www.ti.com

Registers

501

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

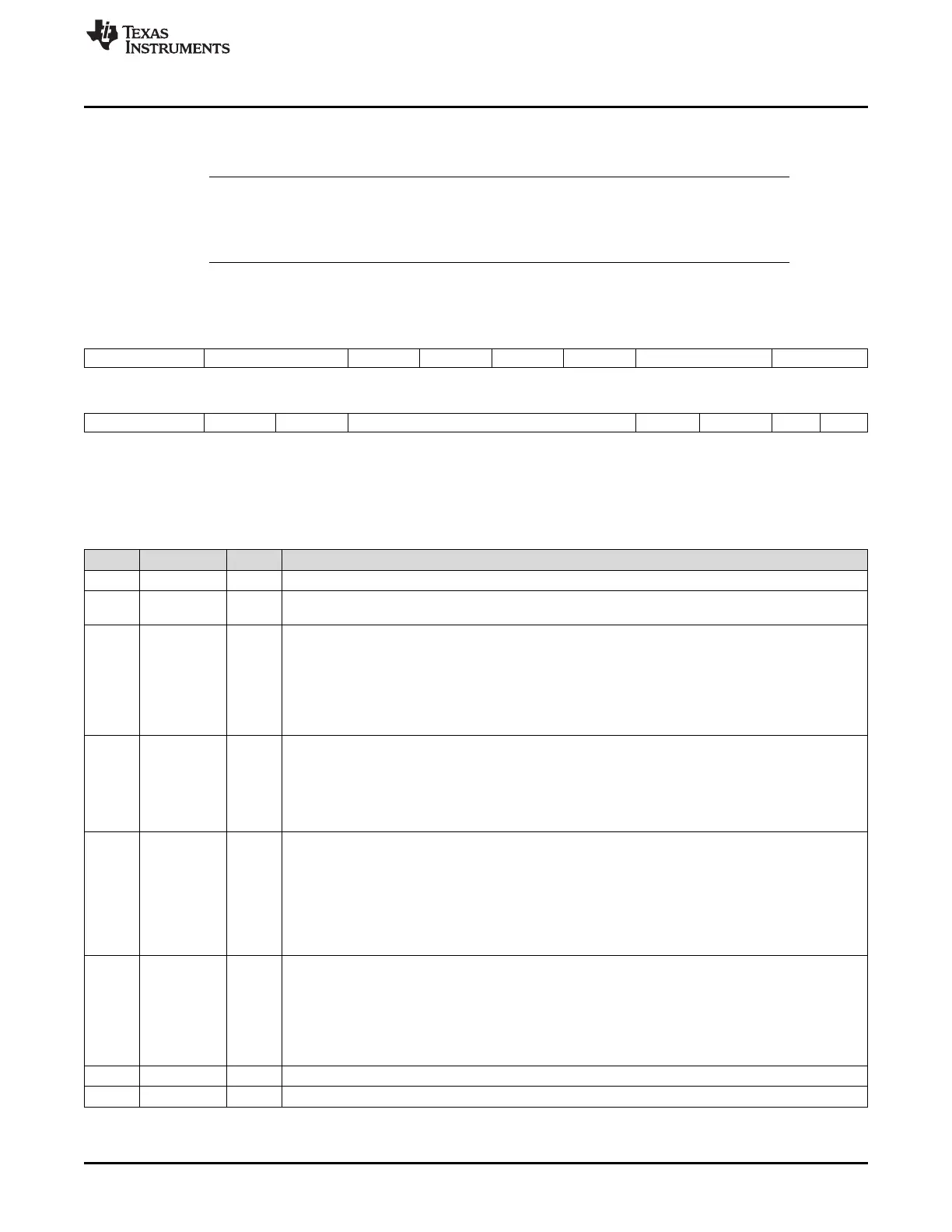

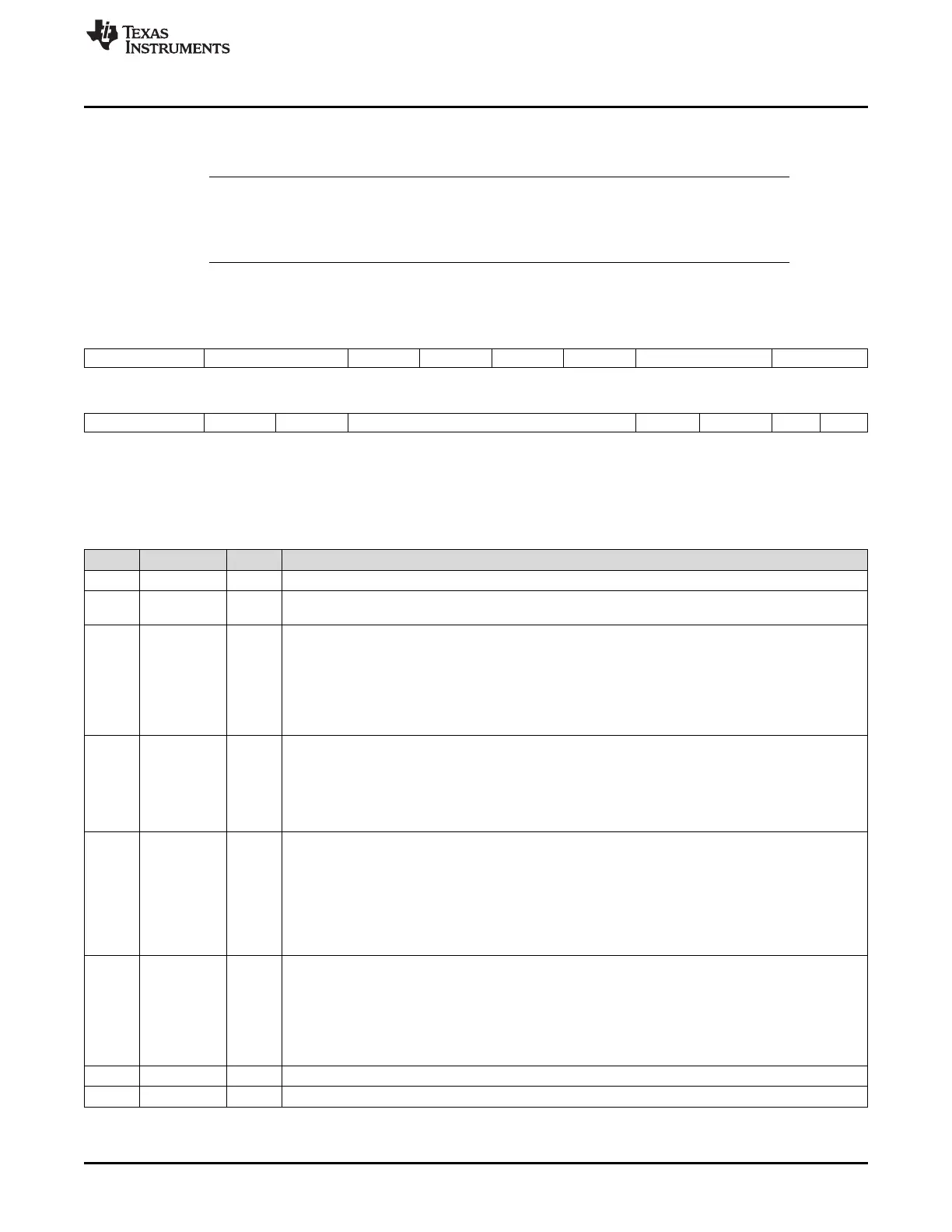

16.4.1.1 Channel Options Parameter (OPT)

The channel options parameter (OPT) is shown in Figure 16-35 and described in Table 16-12.

NOTE: The TCC field in OPT is a 6-bit field and can be programmed for any value between 0-64.

For devices with 32 DMA channels, the TCC field should have a value between 0 to 31 so

that it sets the appropriate bits (0 to 31) in the interrupt pending register (IPR) (and can

interrupt the CPU(s) on enabling the interrupt enable register (IER) bits (0-31)).

Figure 16-35. Channel Options Parameter (OPT)

31 28 27 24 23 22 21 20 19 18 17 16

Reserved PRIVID ITCCHEN TCCHEN ITCINTEN TCINTEN Reserved TCC

R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0

15 12 11 10 8 7 4 3 2 1 0

TCC TCCMOD FWID Reserved STATIC SYNCDIM DAM SAM

R/W-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 16-12. Channel Options Parameters (OPT) Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reserved

27-24 PRIVID 0-Fh Privilege identification for the external host/CPU/DMA that programmed this PaRAM set. This value is

set with the EDMA3 master’s privilege identification value when any part of the PaRAM set is written.

23 ITCCHEN Intermediate transfer completion chaining enable.

0 Intermediate transfer complete chaining is disabled.

1 Intermediate transfer complete chaining is enabled.

When enabled, the chained event register (CER) bit is set on every intermediate chained transfer

completion (upon completion of every intermediate TR in the PaRAM set, except the final TR in the

PaRAM set). The bit (position) set in CER is the TCC value specified.

22 TCCHEN Transfer complete chaining enable.

0 Transfer complete chaining is disabled.

1 Transfer complete chaining is enabled.

When enabled, the chained event register (CER) bit is set on final chained transfer completion (upon

completion of the final TR in the PaRAM set). The bit (position) set in CER is the TCC value specified.

21 ITCINTEN Intermediate transfer completion interrupt enable.

0 Intermediate transfer complete interrupt is disabled.

1 Intermediate transfer complete interrupt is enabled.

When enabled, the interrupt pending register (IPR) bit is set on every intermediate transfer completion

(upon completion of every intermediate TR in the PaRAM set, except the final TR in the PaRAM set).

The bit (position) set in IPR is the TCC value specified. In order to generate a completion interrupt to

the CPU, the corresponding IER[TCC] bit must be set to 1.

20 TCINTEN Transfer complete interrupt enable.

0 Transfer complete interrupt is disabled.

1 Transfer complete interrupt is enabled.

When enabled, the interrupt pending register (IPR) bit is set on transfer completion (upon completion of

the final TR in the PaRAM set). The bit (position) set in IPR is the TCC value specified. In order to

generate a completion interrupt to the CPU, the corresponding IER[TCC] bit must be set to 1.

19 Reserved 0 Reserved. Always write 0 to this bit.

18 Reserved 0 Reserved

Loading...

Loading...