www.ti.com

Registers

887

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Host Port Interface (HPI)

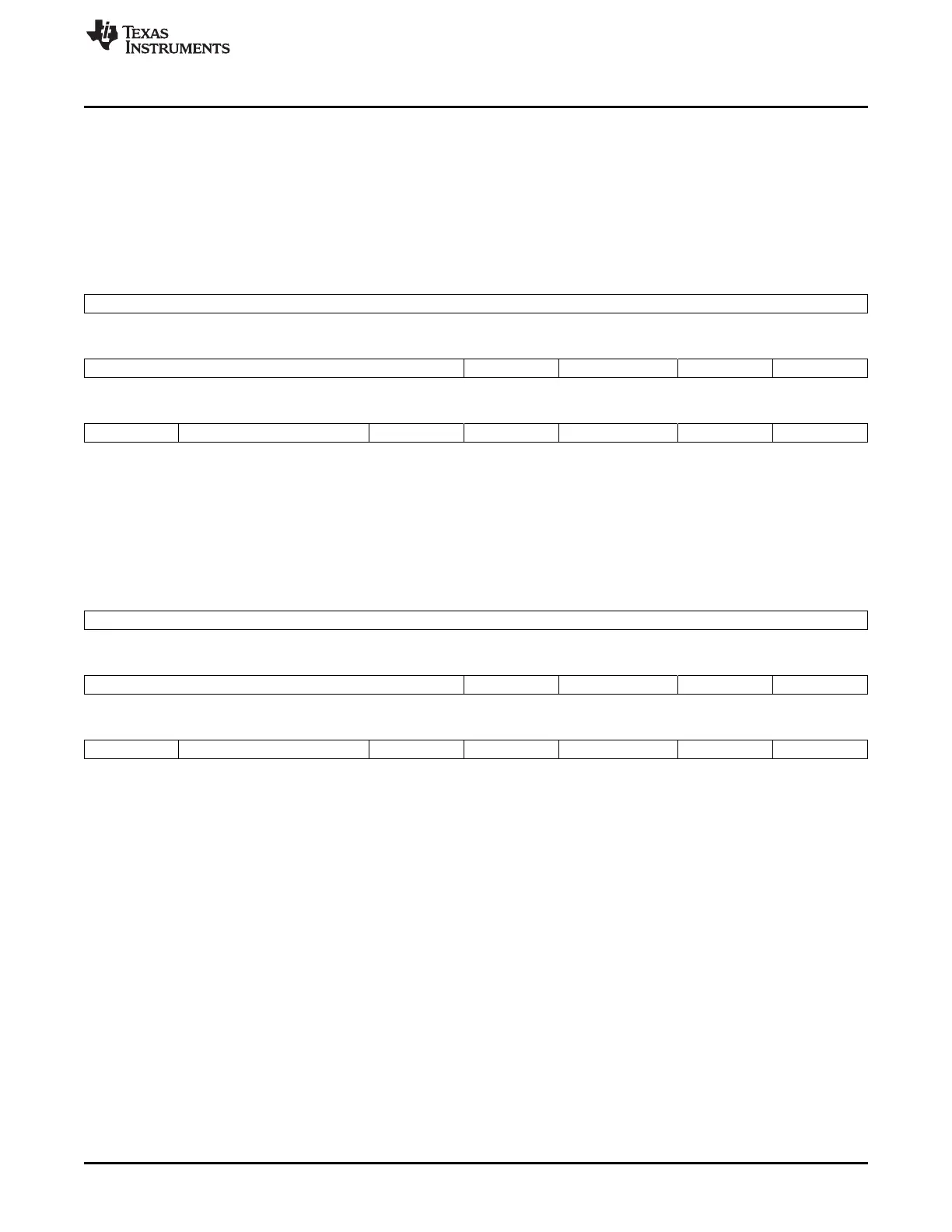

21.3.8 Host Port Interface Control Register (HPIC)

The host port interface control register (HPIC) stores configuration and control information for the HPI. As

shown in Figure 21-24 and Figure 21-25 and described in Table 21-14, the host and CPU do not have the

same access permissions. The host has full read/write access; the CPU has primarily read-only access,

but with the exception that the CPU can write 1 to the HINT bit to generate an interrupt to the host.

Figure 21-24. Host Port Interface Control Register (HPIC)–Host Access Permissions

31 16

Reserved

R-0

15 12 11 10 9 8

Reserved HPIASEL Reserved DUALHPIA HWOBSTAT

R-0 R/W-0 R/W-0 R/W-0 R-0

7 6 5 4 3 2 1 0

HPIRST Reserved FETCH Reserved HINT DSPINT HWOB

R-1 R-2h R/W-0 R-1 R/W-1 (Host)

R/W1C-0 (CPU)

R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect); -n = value after reset

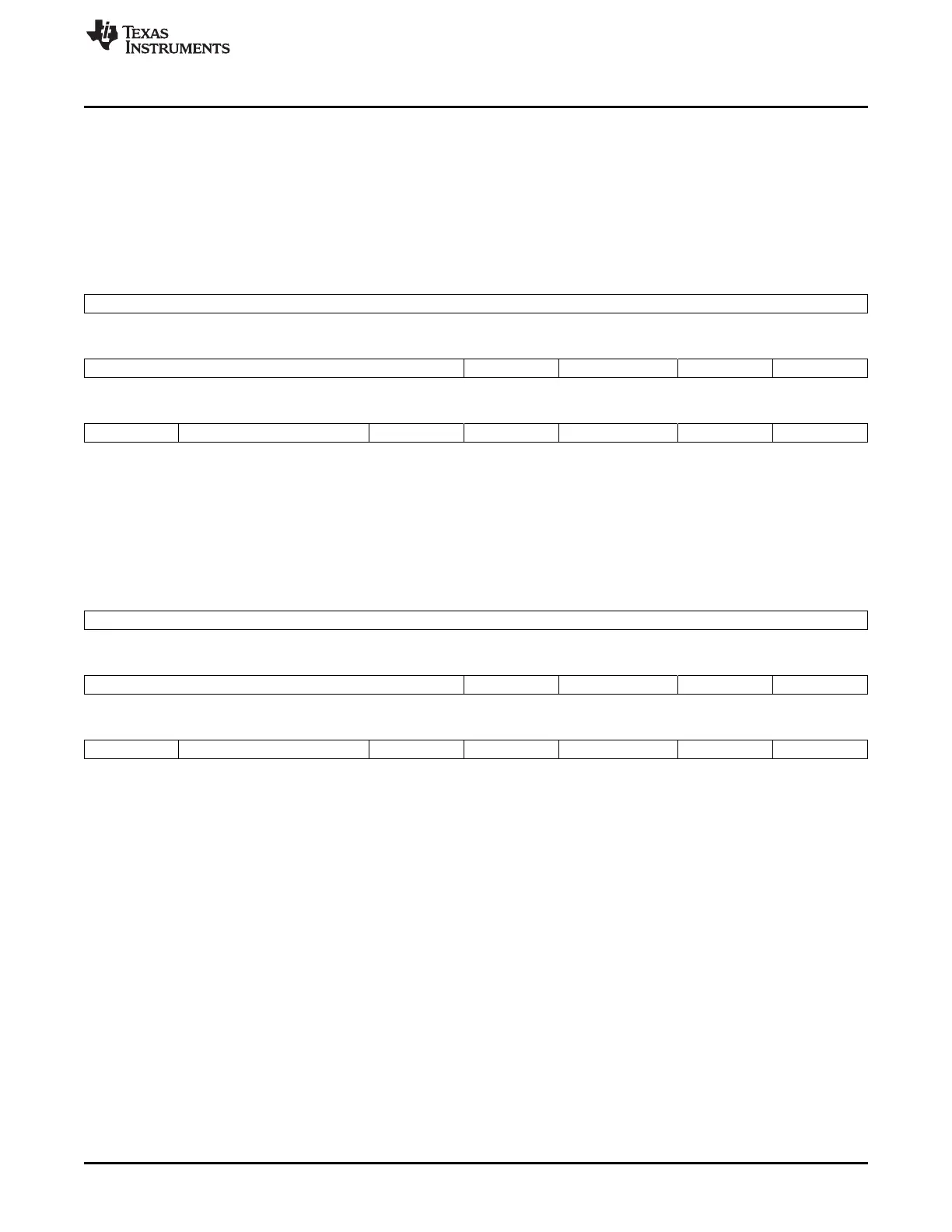

Figure 21-25. Host Port Interface Control Register (HPIC)–CPU Access Permissions

31 16

Reserved

R-0

15 12 11 10 9 8

Reserved HPIASEL Reserved DUALHPIA HWOBSTAT

R-0 R-0 R-0 R-0 R-0

7 6 5 4 3 2 1 0

HPIRST Reserved FETCH Reserved HINT DSPINT HWOB

R/W-1 R-2h R-0 R-1 R/W-1 (Host)

R/W1C-0 (CPU)

R/W-0 R-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect); -n = value after reset

Loading...

Loading...