Transmit

formatunit

Receive

formatunit

Transmit

state

machine

Transmit

TDM

sequencer

Receive

state

machine

Receive

TDM

sequencer

Control

32

32

32

32

Serializer0

Serializer1

Serializern

AXR0

AXR1

AXRn

(A)

Clock

generator

Framesync

generator

AUXCLK

Clock

generator

Framesync

generator

AUXCLK

Transmit

Receive

Control

GPIO

Errorcheck

ACLKX

AHCLKX

AFSX

AFSR

AHCLKR

ACLKR

AMUTE

AMUTEIN

(B)

AXEVT

AREVT

AXINT

ARINT

DMA events

Interrupts

Clockcheck

circuit

Audio

FIFO

WFIFO

RFIFO

FIFO

CONTROL/

STATUS

AXEVT

AREVT

DMA events

DMA bus

Peripheralconfigurationbus

Pinfunctioncontrol

www.ti.com

984

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Multichannel Audio Serial Port (McASP)

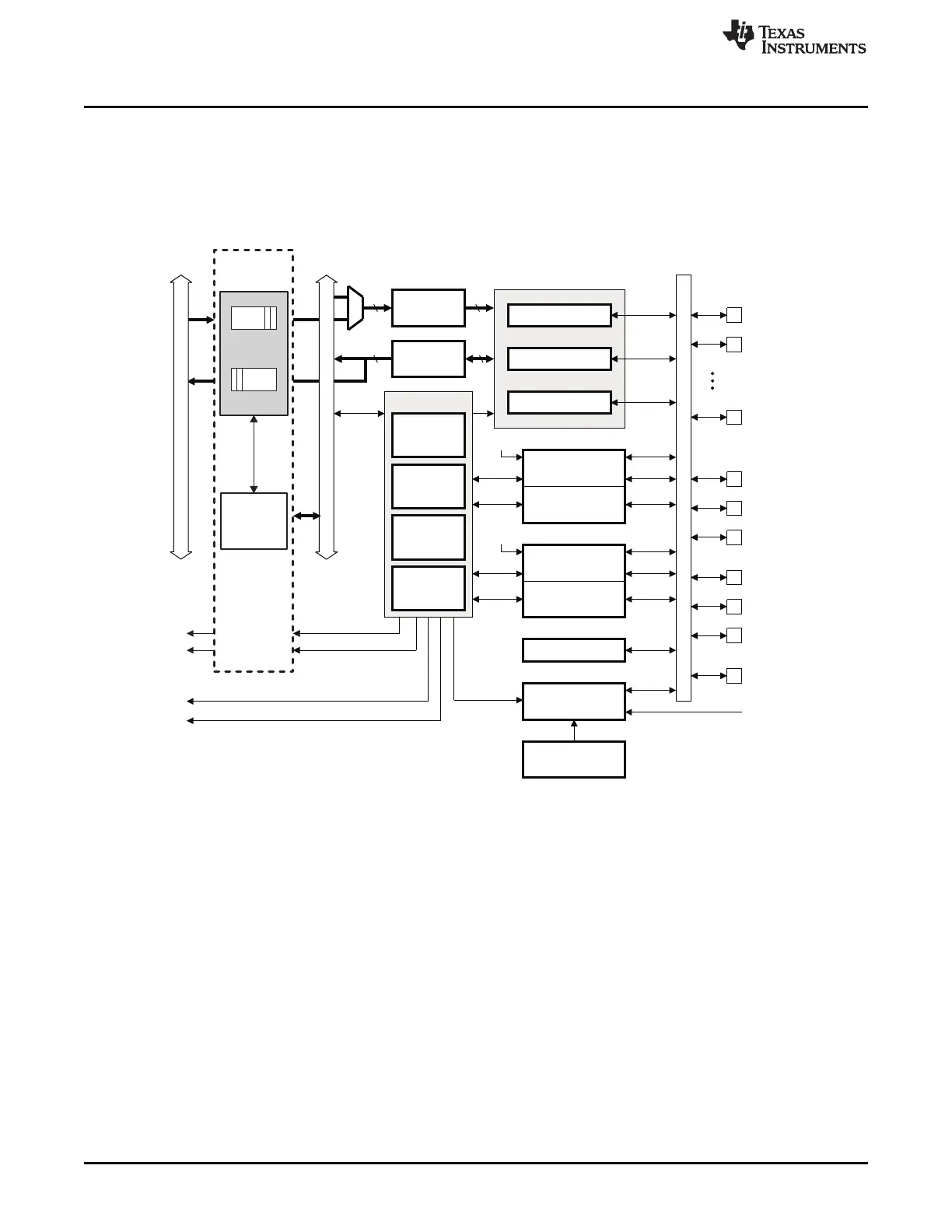

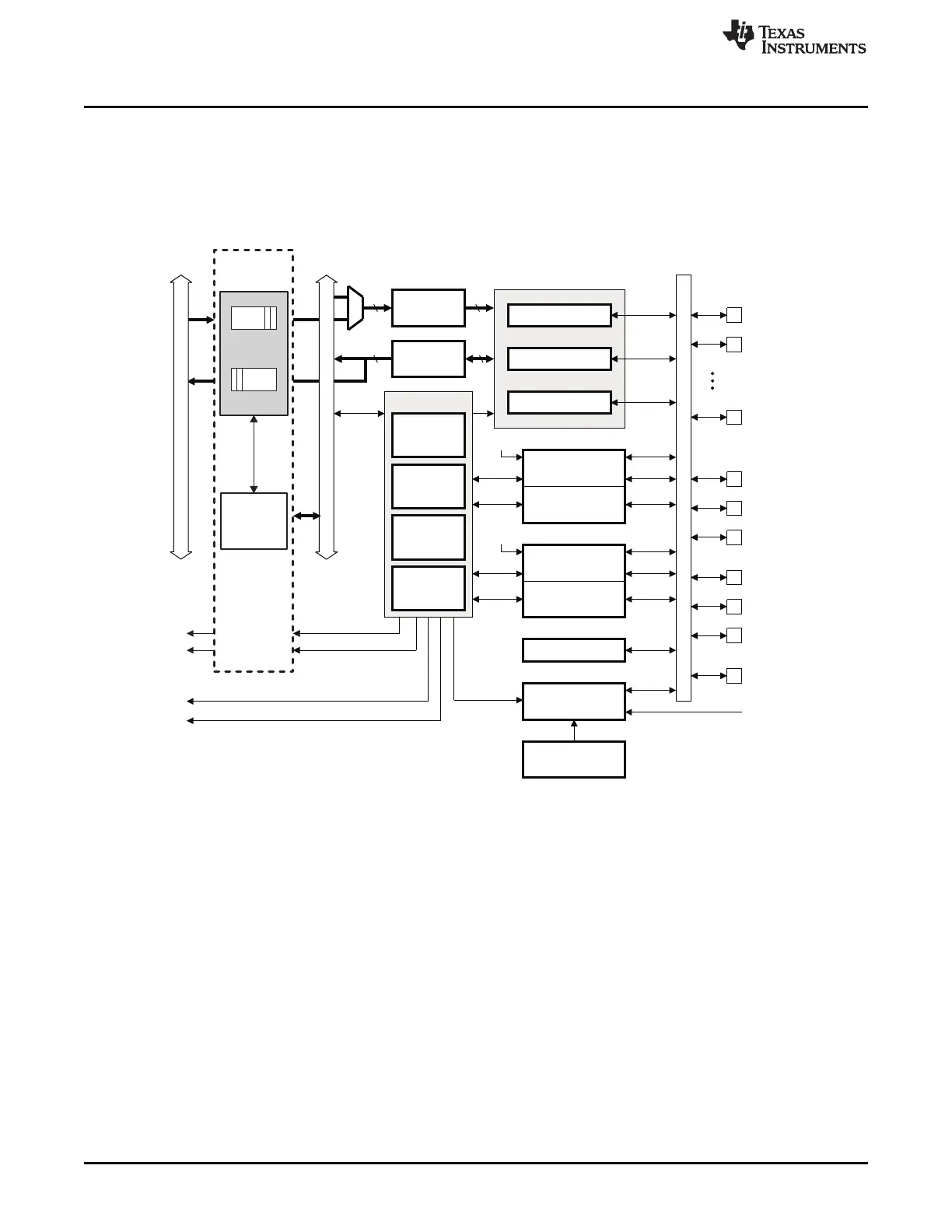

24.0.18 Functional Block Diagram

A block diagram of the McASP is shown in Figure 24-1. The McASP has independent receive/transmit

clock generators and frame sync generators.

Figure 24-1. McASP Block Diagram

A McASP0 has up to 16 serial data pins, n = 15; McASP1 has up to 12 serial data pins, n = 11;

McASP2 has up to 4 serial data pins, n = 3.

B One of the DSP's external pins, see your device-specific data manual.

Loading...

Loading...