0000 0000 0000 00

31 1314

PAENTRY

45 02 1

TR WORD

00QCHMAPn

Parameter set 0

Parameter set 1

Parameter set 3

Parameter set 2

Parameter set n−1

Parameter set n−2

Set

#

0

1

2

3

n−2

n−1

DSTBIDX

BCNTRLD

Rsvd

DSTCIDX

CCNT

SRCCIDX

LINK

SRCBIDX

DST

BCNT ACNT

SRC

OPT

PaRAM PaRAM set

+0h

+4h

+8h

+Ch

Byte

address

+1Ch

+18h

+14h

+10h

offset

00 0000 011 1 11

Parameter set nn

www.ti.com

Architecture

463

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Enhanced Direct Memory Access (EDMA3) Controller

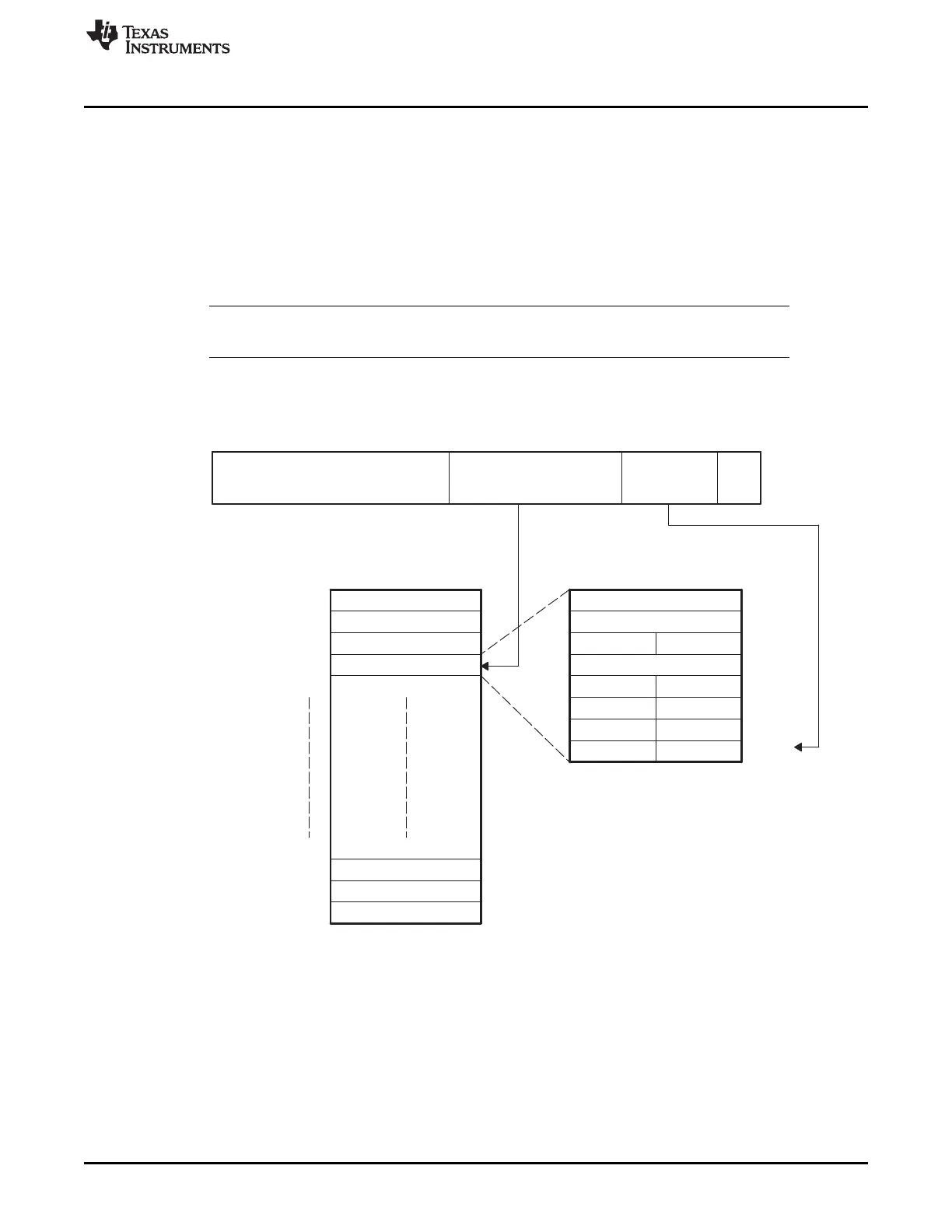

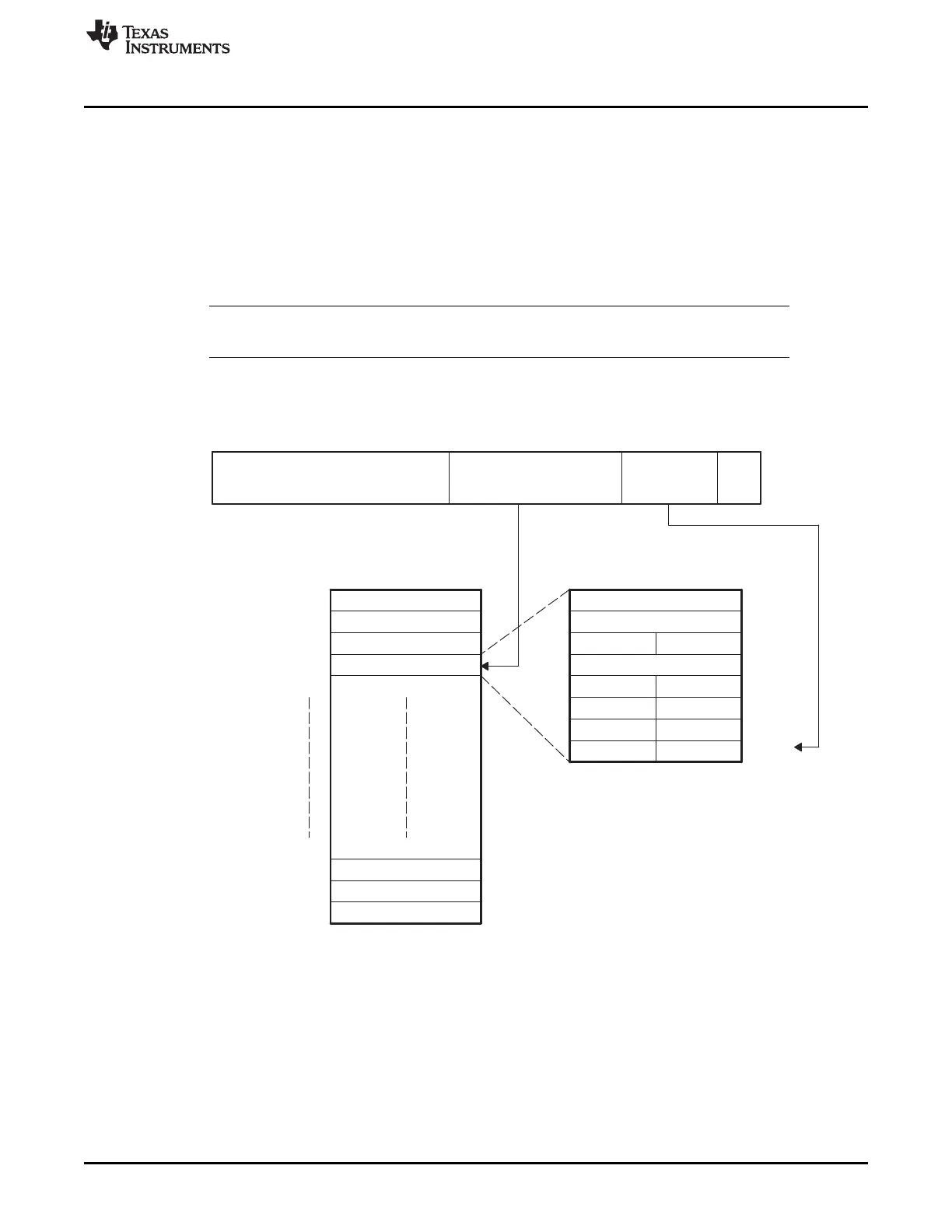

16.2.6.2 QDMA Channel to PaRAM Mapping

The mapping between the QDMA channels and the PaRAM sets is programmable .The QDMA channel n

mapping register (QCHMAPn) in the EDMA3CC provides programmability for the QDMA channels to be

mapped to any of the PaRAM sets in the PaRAM memory map. Figure 16-10 illustrates the use of

QCHMAP.

Additionally, QCHMAP allows you to program the trigger word in the PaRAM set for the QDMA channel. A

trigger word is one of the 8 words in the PaRAM set. For a QDMA transfer to occur, a valid TR

synchronization event for EDMA3CC is a write to the trigger word in the PaRAM set pointed to by

QCHMAP for a particular QDMA channel.

NOTE: By default, QDMA channels are mapped to PaRAM set 0. Care must be taken to

appropriately remap PaRAM set 0 before it is used.

Figure 16-10. QDMA Channel to PaRAM Mapping

Note: n is the number of PaRAM sets supported in the EDMA3CC for a specific device.

Loading...

Loading...