HPI

USB0

USB0

SCR7

DSP MDMA

EDMA3 TC0

rd

wr

EDMA3 TC1

wr

SCR1

BR3 BR4

SCR2

DSP CFG

DSP SDMA (L1D/L2)

BR13

MPU1

BR19

SCR9

LCDC

BR20

EMIFB

SCR5

PSC0

PLLC

SYSCFG

BR5

Clock Domain: SYSCLK4

[CPU/4 Synchronous]

SCR6

Timer64P0

S

Timer64P1

S

I2C0

S

RTC

S

BR6

Async 2 Clock Domain

BR7

EMIFA

Async 1 Clock Domain

SCR4

MMC/SD0

SPI0

UART0

EDMA3 TC0

EDMA3 TC1

SCR12

USB0 Cfg

HPI Cfg

SPI1

LCDC

SCR13

Clock Domain: SYSCLK4

[CPU/4 Synchronous]

EMAC

EMAC MDIO

USB1 Cfg

GPIO

PSC1

I2C1

BR18

SCR11

UART1

UART2

McASP0

McASP1

McASP2

SCR10

eHRPWM0

eHRPWM1

eHRPWM2

eCAP0

eCAP1

eCAP2

eQEP0

eQEP1

EDMA3 CC

EDMA3 CC

Legend:

32-Bit BUS

64-Bit BUS

IP Module

Synchronous Bridge

Asynchronous Bridge

SCR

Paths with dashed lines cross the subchip boundary

BR9

BR10

BR11

BR12

EMAC

USB1

SCR8

BR13

BR14

BR15

(A)

(A)

(A)

(A)

(A)

(A)

(A)

(A)

rd

128k Shared RAM

(A)

MPU2

PRU0

PRU1

PRU Cfg

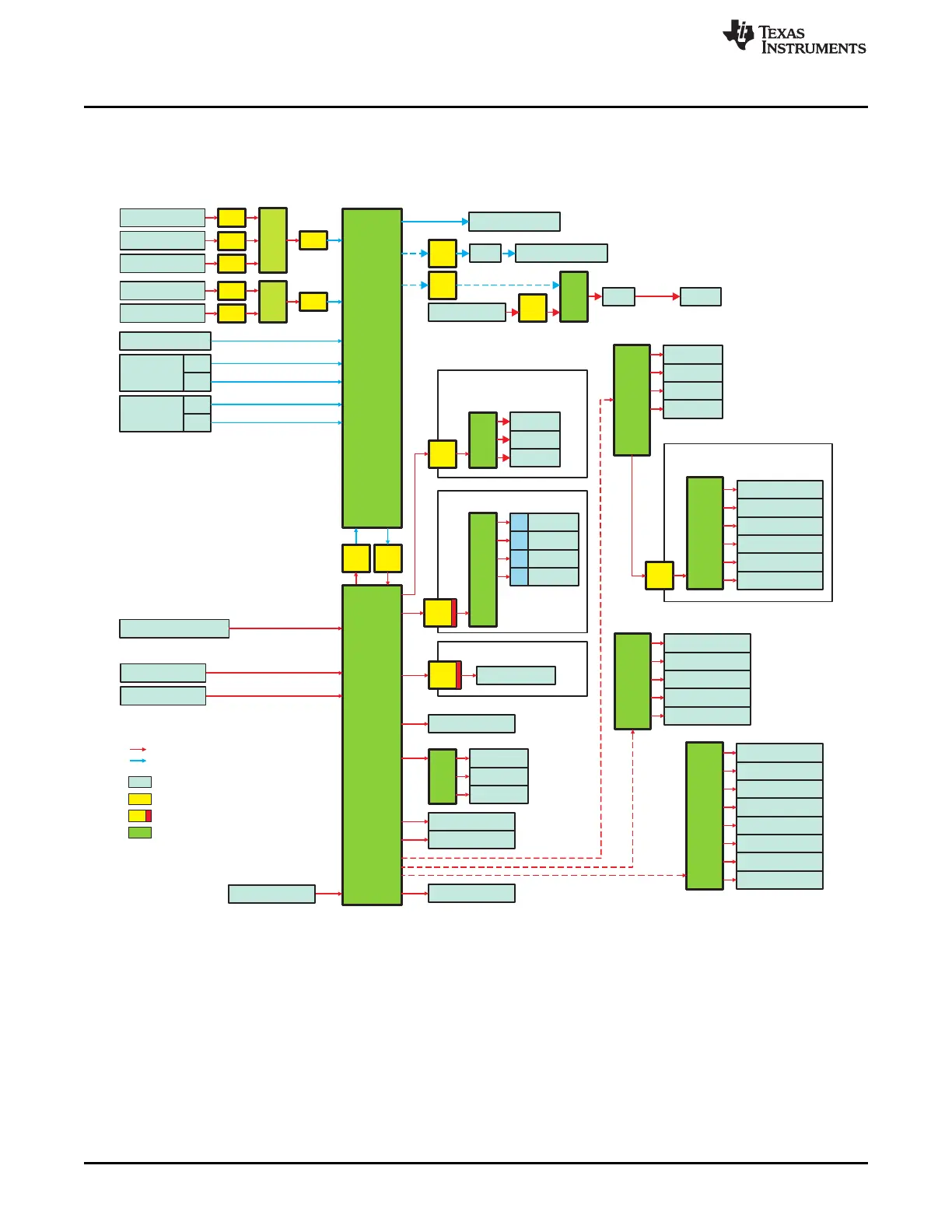

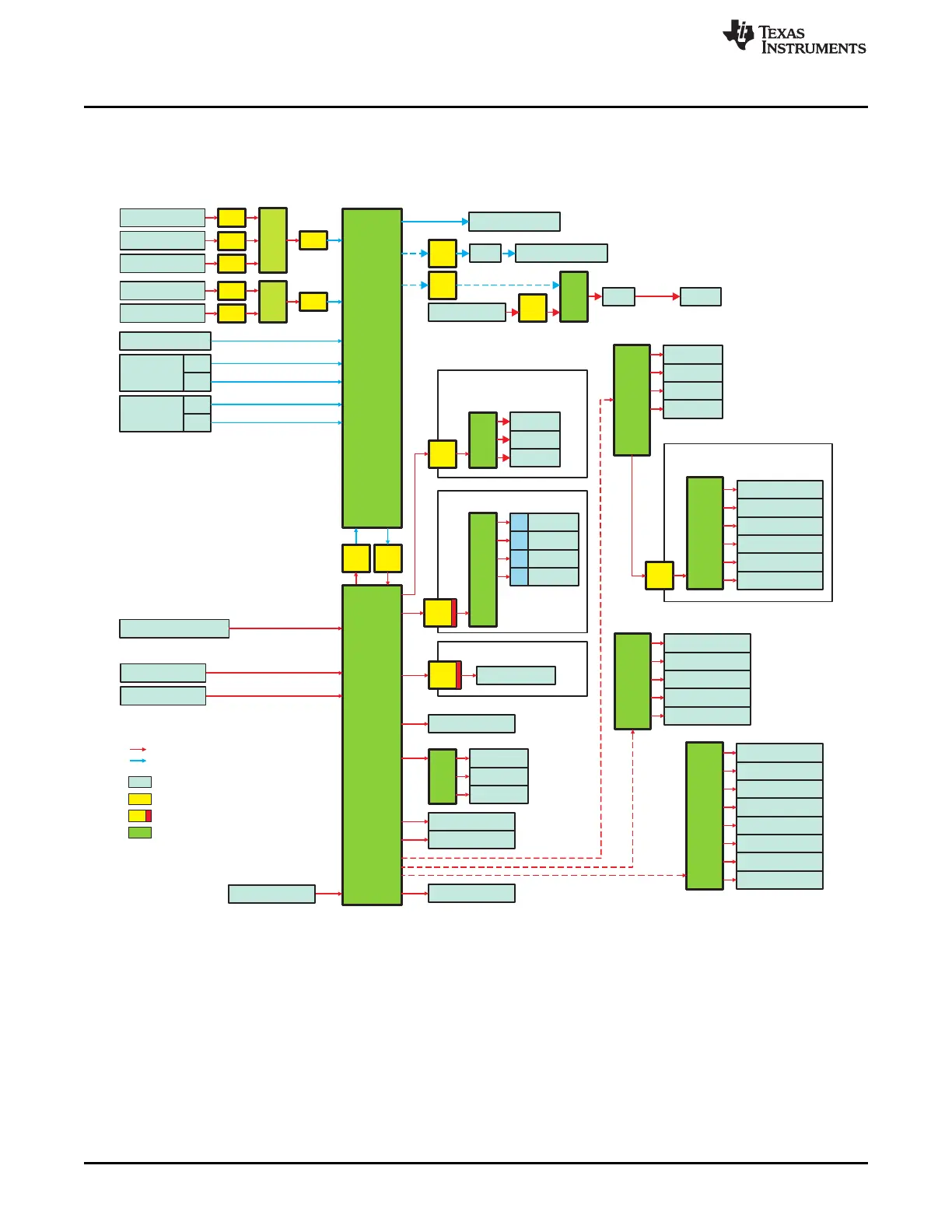

System Interconnect Block Diagram

www.ti.com

78

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

System Interconnect

3.2 System Interconnect Block Diagram

Figure 3-1 shows a system interconnect block diagram.

Figure 3-1. System Interconnect Block Diagram

A This peripheral is not supported on the C6745 DSP.

Loading...

Loading...