SYSCFG Registers

www.ti.com

236

SPRUH91D–March 2013–Revised September 2016

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

System Configuration (SYSCFG) Module

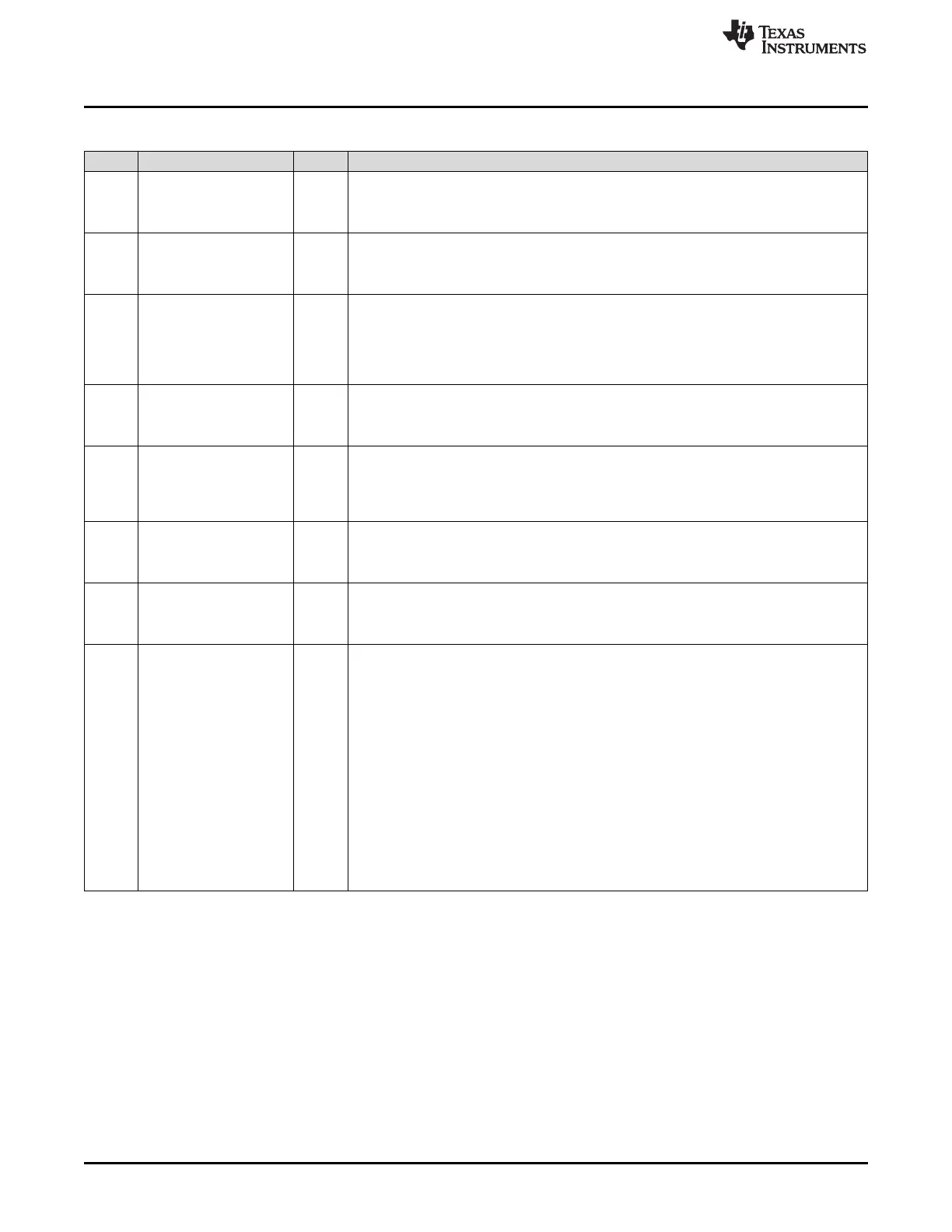

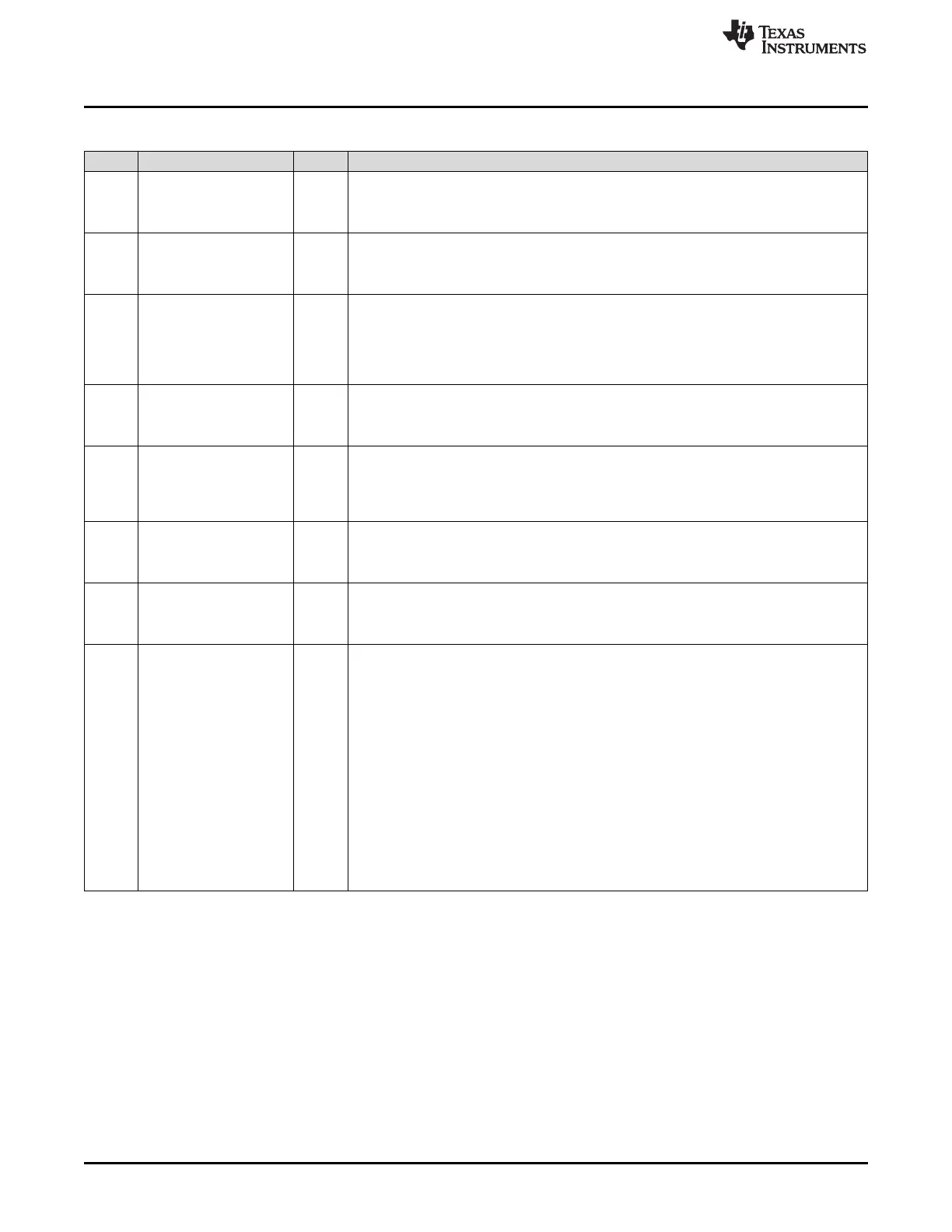

Table 10-47. Chip Configuration 2 Register (CFGCHIP2) Field Descriptions (continued)

Bit Field Value Description

10 USB0PHYPWDN USB2.0 PHY operation state control.

0 USB2.0 PHY is enabled and is in operating state (normal operation).

1 USB2.0 PHY is disabled and powered down.

9 USB0OTGPWRDN USB2.0 OTG subsystem (SS) operation state control.

0 OTG SS is enabled and is in operating state (normal operation).

1 OTG SS is disabled and is powered down.

8 USB0DATPOL USB2.0 differential data lines polarity selector.

0 Differential data polarities are inverted (USB_DP is connected to D- and USB_DM is

connected to D+).

1 Differential data polarity are not altered (USB_DP is connected to D+ and USB_DM is

connected to D-).

7 USB1SUSPENDM USB1.1 suspend mode. This peripheral is not supported on the C6745 DSP.

0 Needs to be 0 whenever USB1.1 PHY is unpowered

1 Enable USB1.1 PHY

6 USB0PHY_PLLON Drives USB2.0 PHY, allowing or preventing it from stopping the 48 MHz clock during

USB SUSPEND.

0 USB2.0 PHY is allowed to stop the 48 MHz clock during USB SUSPEND.

1 USB2.0 PHY is prevented from stopping the 48 MHz clock during USB SUSPEND

5 USB0SESNDEN USB2.0 Session End comparator enable.

0 Session End comparator is disabled.

1 Session End comparator is enabled.

4 USB0VBDTCTEN USB2.0 VBUS line comparators enable.

0 All VBUS line comparators are disabled.

1 All VBUS line comparators are enabled.

3-0 USB0REF_FREQ USB2.0 PHY reference clock input frequencies.

0 Reserved

1h 12 MHz

2h 24 MHz

3h 48 MHz

4h 19.2 MHz

5h 38.4 MHz

6h 13 MHz

7h 26 MHz

8h 20 MHz

9h 40 MHz

Ah-Fh Reserved

Loading...

Loading...