www.ti.com

General-Purpose Input/Output (GPIO)

119

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

The GPADIR and GPBDIR registers control the direction of the pins when they are configured as a GPIO

in the appropriate MUX register. The direction register has no effect on pins configured as peripheral

functions.

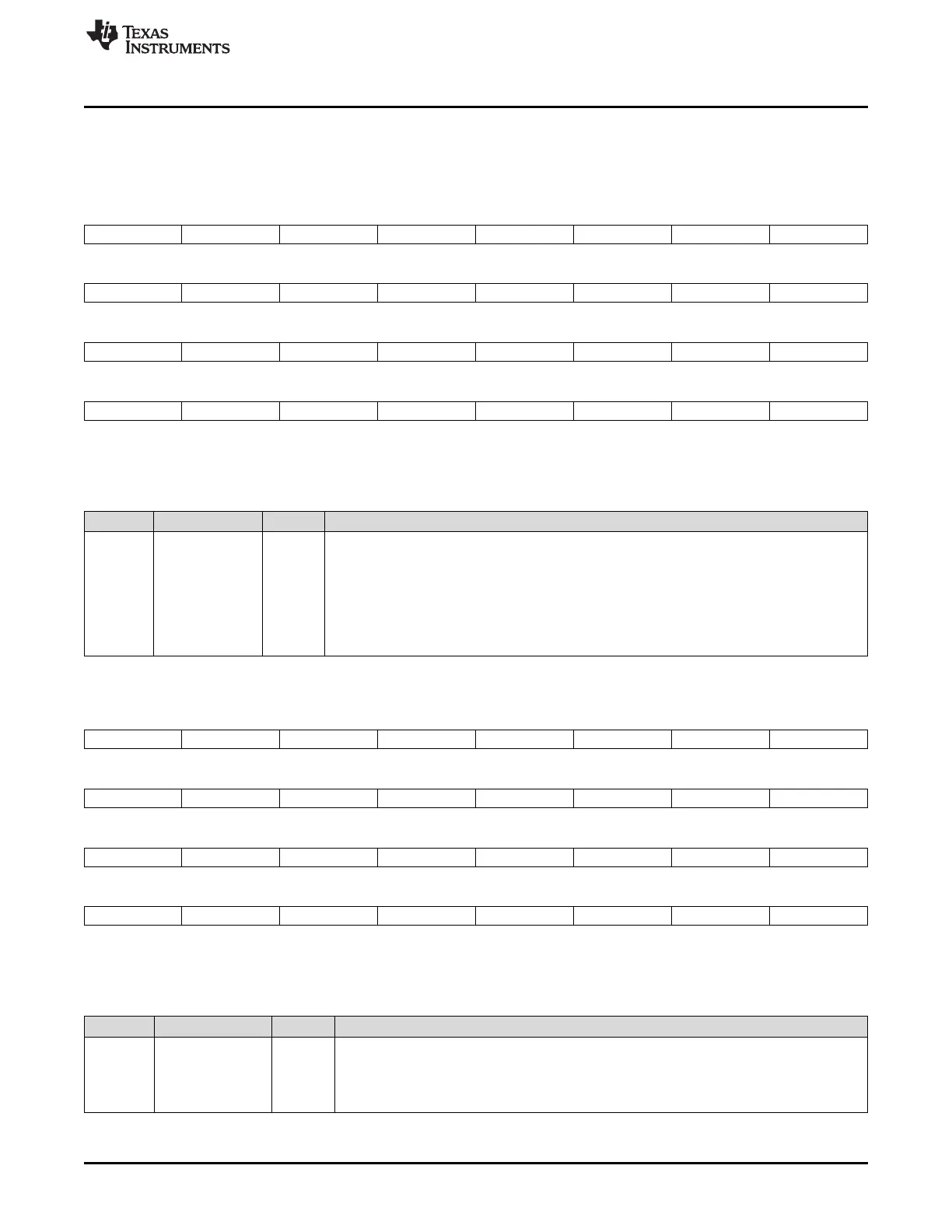

Figure 1-59. GPIO Port A Direction (GPADIR) Register

31 30 29 28 27 26 25 24

GPIO31 GPIO30 GPIO29 GPIO28 GPIO27 GPIO26 GPIO25 GPIO24

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

23 22 21 20 19 18 17 16

GPIO23 GPIO22 GPIO21 GPIO20 GPIO19 GPIO18 GPIO17 GPIO16

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9 GPIO8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

Table 1-62. GPIO Port A Direction (GPADIR) Register Field Descriptions

Bits Field Value Description

(1)

31-0 GPIO31-GPIO0 Controls direction of GPIO Port A pins when the specified pin is configured as a GPIO in the

appropriate GPAMUX1 or GPAMUX2 register.

0 Configures the GPIO pin as an input. (default)

1 Configures the GPIO pin as an output

The value currently in the GPADAT output latch is driven on the pin. To initialize the GPADAT

latch prior to changing the pin from an input to an output, use the GPASET, GPACLEAR, and

GPATOGGLE registers.

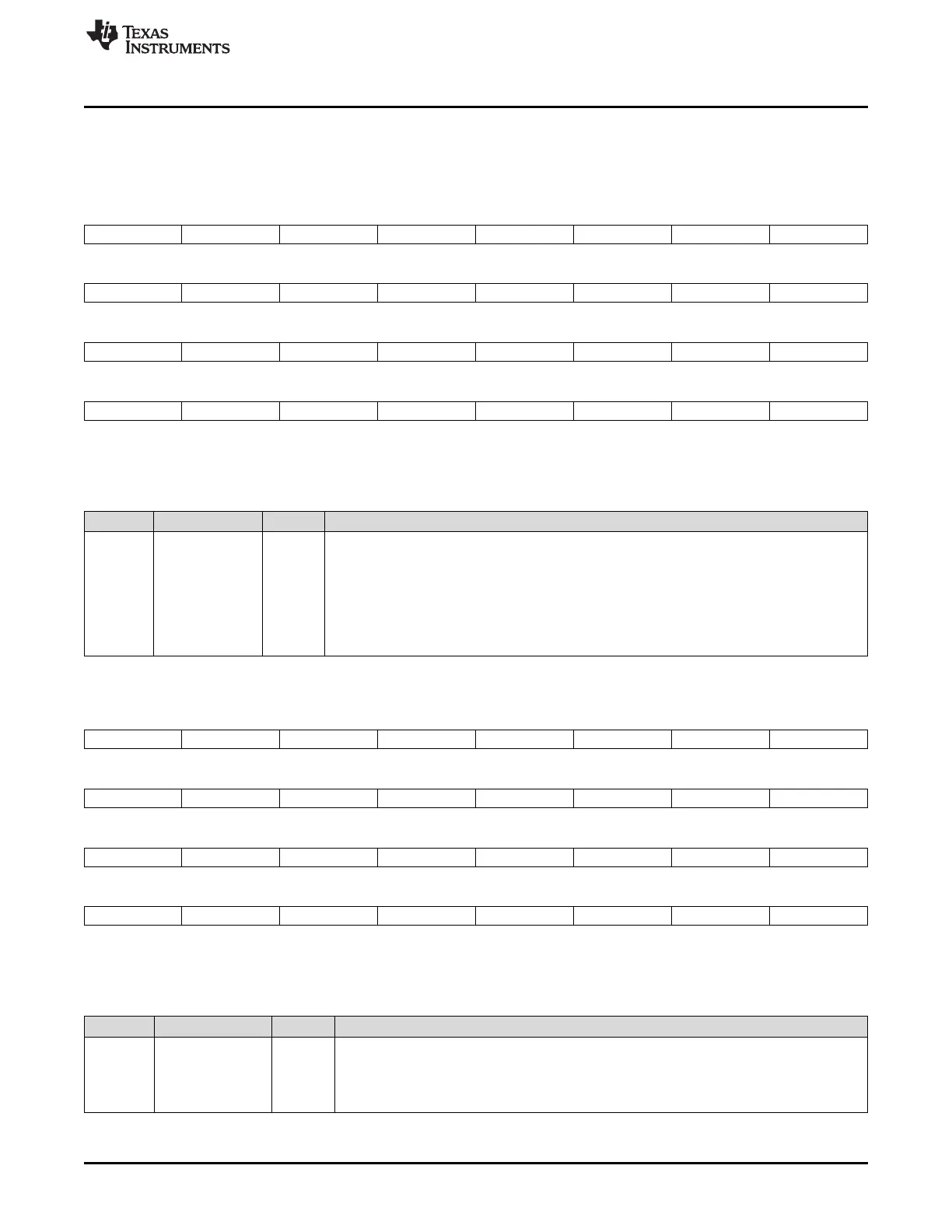

Figure 1-60. GPIO Port B Direction (GPBDIR) Register

31 30 29 28 27 26 25 24

GPIO63 GPIO62 GPIO61 GPIO60 GPIO59 GPIO58 GPIO57 GPIO56

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

23 22 21 20 19 18 17 16

GPIO55 GPIO54 GPIO53 GPIO52 GPIO51 GPIO50 GPIO49 GPIO48

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

GPIO47 GPIO46 GPIO45 GPIO44 GPIO43 GPIO42 GPIO41 GPIO40

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

GPIO39 GPIO38 GPIO37 GPIO36 GPIO35 GPIO34 GPIO33 GPIO32

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

Table 1-63. GPIO Port B Direction (GPBDIR) Register Field Descriptions

Bits Field Value Description

(1)

31-0 GPIO63-GPIO32 Controls direction of GPIO pin when GPIO mode is selected. Reading the register returns the

current value of the register setting

0 Configures the GPIO pin as an input. (default)

1 Configures the GPIO pin as an output

Loading...

Loading...